Komputer na układach TTL, czyli znów wszystko na jedną kartę… (część 4)

Artykuł przybliża konteksty obsługi pamięci operacyjnej. Można się również z niego dowiedzieć o różnych trybach adresowania, które będą zaimplementowane w procesorze KYRON.

To jest kolejny artykuł serii dotyczącej projektu potężnego komputera TTL. Wcześniejsze odcinki to:

• Kalkulator na układach TTL, czyli rozgrzewka przed… – D100

• Komputer na układach TTL, czyli znów wszystko na jedną kartę… (1) – D101

• Komputer na układach TTL, czyli znów wszystko na jedną kartę… (2) – D102

• Komputer na układach TTL, czyli znów wszystko na jedną kartę… (3) – D103

Konteksty obsługi pamięci RAM bardziej ogólnie

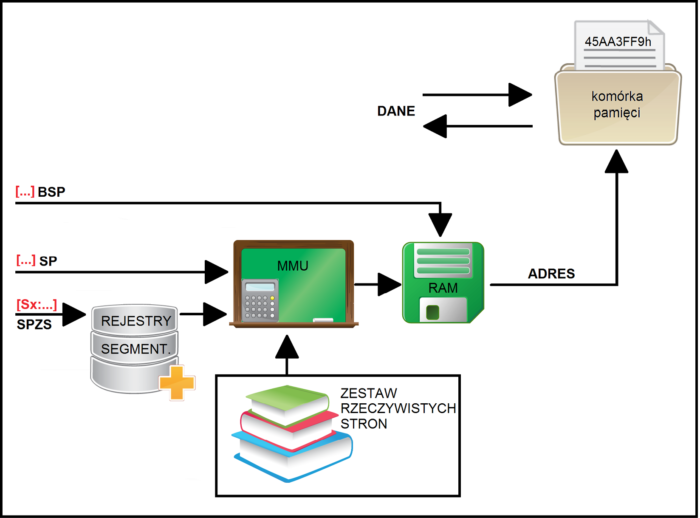

Już na samym początku muszę wspomnieć, że jakiekolwiek adresowanie argumentów związane z pamięcią RAM w moim komputerze wykorzystuje jeden z trzech kontekstów ją obsługujących. Przedstawia to symbolicznie rysunek 1.

Dokładna logika tych konspektów będzie omówiona w kolejnym odcinku. Istnieją trzy możliwości:

BSP – adresowanie pamięci bez jej stronicowania, czyli najbardziej podstawowe. Zawartość zmiennej adresowej znajdująca się w […] będzie wskazywała liniowy, prawdziwy adres 32-bitowej komórki pamięci. Co ważne, możliwość ta będzie dostępna tylko i wyłącznie w TRYBIE NADZORCY. Zdecydowałem się na taki krok ze względu na to, że w obszarze rzeczywistym o pewnej wielkości będzie rezydował system operacyjny. Żaden program użytkownika nie będzie miał tam dostępu, ewentualny błąd w aplikacji użytkownika nie spowoduje uszkodzenia systemu operacyjnego, a co za tym idzie, nie spowoduje niestabilności w jego pracy lub, w najgorszym przypadku, zawieszenia komputera. Oczywiście, gdy system operacyjny będzie zawierał jakieś błędy to on wtedy będzie źródłem dziwnych i trudnych do wytłumaczenia problemów. Czas pokaże…

SP – adresowanie pamięci wykorzystujące stronicowanie. Kontekst ten będzie dostępny w TRYBIE NADZORCY oraz w TRYBIE UŻYTKOWNIKA z pewnymi wyjątkami dotyczącymi rejestrów dedykowanych tylko i wyłącznie dla trybu nadzorcy. W tej metodzie wykorzystywana jest jednostka MMU. Jednostka MMU ma załadowane strony, które określają rzeczywisty adres w pamięci operacyjnej. Każdy niezależny proces, czy to proces nadzorcy, czy użytkownika, w tym trybie ma określoną pulę stron, niezależnych stron. Strony te przydziela system operacyjny poprzez odpowiednie wywołanie systemowe. To system operacyjny dba o to, aby translatowane adresy nie dublowały się, aby żaden proces nie nałożył się na inny, co spowodowałoby jego uszkodzenie i niestabilność. Wszystkie te szczegóły, tak jak wspomniałem, omówię w kolejnym odcinku.

Zaletą tego trybu jest to, że każdy proces ma zestaw adresu pozornego od zera do wartości maksymalnej (zależy ile miał przydzielonych stron, o ile ich poprosił). Jest to tak zwany adres logiczny. Takie posunięcie ułatwia tworzenie oprogramowania – nie musimy się zastanawiać, w którym konkretnym miejscu w rzeczywistej pamięci RAM program się znajdzie – może się znaleźć w różnych miejscach, może to być struktura nieciągła, lecz od strony jego adresu zawsze będzie to przedział liniowy, chronologiczny. W każdym programie załadowanym w ten sposób, wszystkie jego odwołania do argumentów znajdujących się w pamięci system operacyjny nie musi dynamicznie przeliczać, zasoby sprzętowe procesora nie są angażowane do tych operacji, procesor nie wie, który konkretny fragment pamięci RAM obsługuje. To właśnie jednostka zarządzania pamięcią MMU konwertuje adresy logiczne […] na prawidłowe adresy rzeczywiste. W skrócie od strony elektronicznej wygląda to następująco:

Jednostka MMU to nic innego jak zestaw statycznych kości pamięci, kości pamięci RAM takich samych jak te, z których się składa właściwa karta pamięci RAM. Pamięci te zawierają strony uprzednio wpisane przez system operacyjny – dwukierunkowa szyna danych służy do programowania tych pamięci oraz do adresowania głównej pamięci RAM. Adres wejściowy, czyli adres logiczny sprzężony jest z wejściami adresowymi pamięci mieszczącej się w module MMU. Każdy proces poprzez adresację najstarszych wejść adresowych pamięci znajdującej się w module MMU wybiera w nich niezależny roboczy obszar. Maksymalna ilość uruchomionych procesów, którą planuję wdrożyć to 32. Na ten moment waham się jeszcze w wyborze docelowych pamięci statycznych. Zależnie od pojemności w bajtach pojedynczej wybranej przeze mnie kostki może być potrzebny jeszcze dodatkowy dekoder 1/n i wtedy pięciobitowa linia związana z wyborem aktywnego procesu w MMU może być podłączona do wejść adresujących dekodera, a nie do najstarszych wejść adresowych pamięci. Na ten moment, temat ten jest jeszcze do przemyślenia, a wszystkie argumenty „za” i „przeciw” są jeszcze w fazie rozważania. Nie sposób ich tu wszystkich przytoczyć.

SPZS – adresowanie pamięci wykorzystujące stronicowanie z segmentacją. Podobnie jak w powyższym podpunkcie, kontekst ten będzie dostępny w TRYBIE NADZORCY oraz w TRYBIE UŻYTKOWNIKA również z pewnymi wyjątkami dotyczącymi rejestrów dedykowanych tylko i wyłącznie do trybu nadzorcy. Tutaj również wykorzystywana jest jednostka MMU, lecz jest ona jakby drugą w kolejności. W pierwszej kolejności prym tutaj wiodą rejestry segmentowe, przypomnijmy: CS, DS, SS, ES. W tym przypadku pojedynczy proces oprócz tego, że posiada swoje przydzielone strony, może też odrębnie obsługiwać do czterech niezależnych obszarów, skategoryzowanych obszarów zawierających te strony. Dokładniejsza semantyka tych rejestrów była opisana w drugim odcinku tego cyklu. A zasadę działania SPZS omówię dokładniej w kolejnym odcinku tego cyklu. W tym momencie przedstawię tylko ogólny zarys jej dobrodziejstwa.

(…)

——– ciach! ——–

To jest tylko fragment artykułu, którego pełna wersja ukazała się w grudniowym numerze czasopisma Zrozumieć Elektronikę (ZE 12/2025). Pełną wersję czasopisma znajdziesz pod tym linkiem. Natomiast niepełna, okrojona wersja, pozwalająca zapoznać się z zawartością numeru ZE 12/2025 znajduje się tutaj.

Rafał Wiśniewski

rafi8112@interia.pl

Uwaga! Wskazówki, jak nabyć pełne wersje dowolnych numerów ZE znajdują się na stronie:

https://piotr-gorecki.pl/n11.