PKE – Praktyczny Kurs Elektroniki (21) Centralka alarmowa

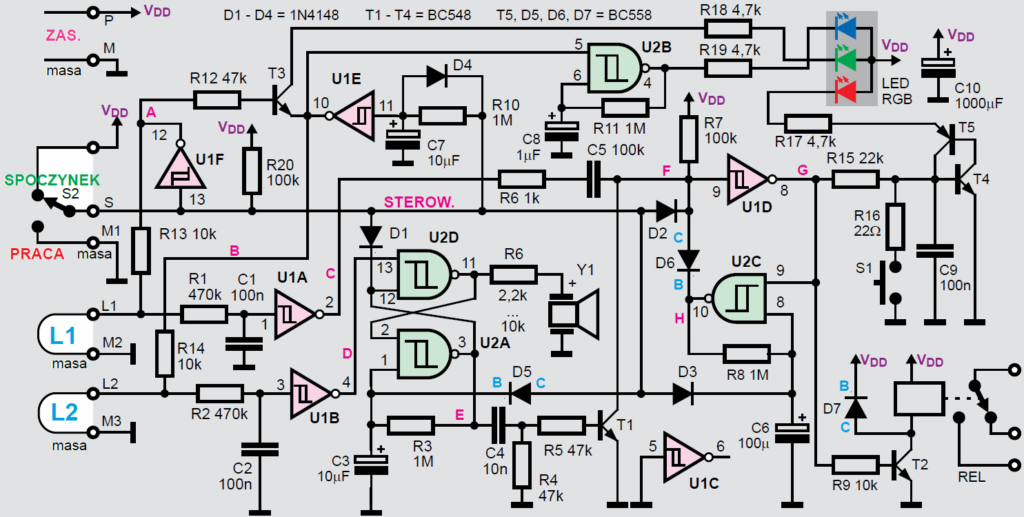

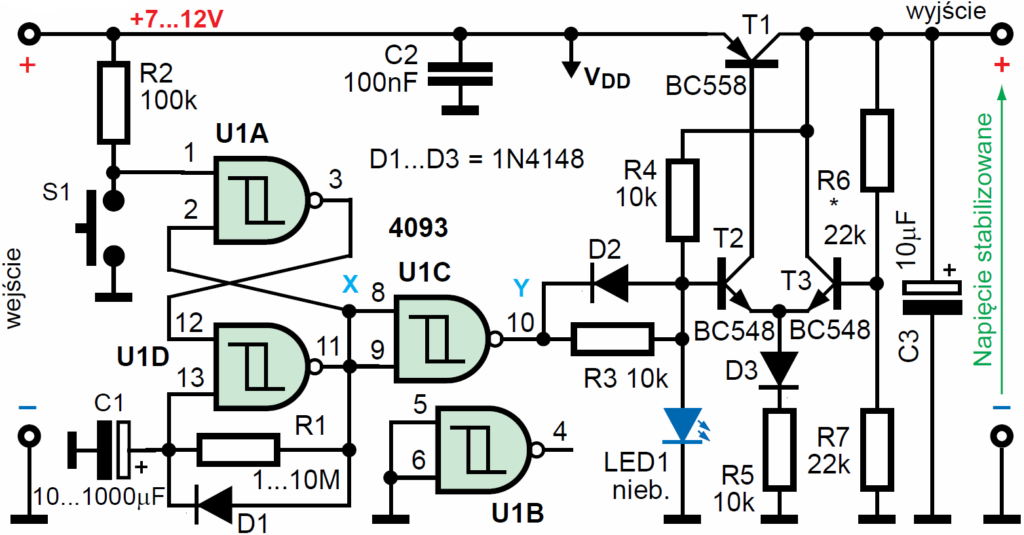

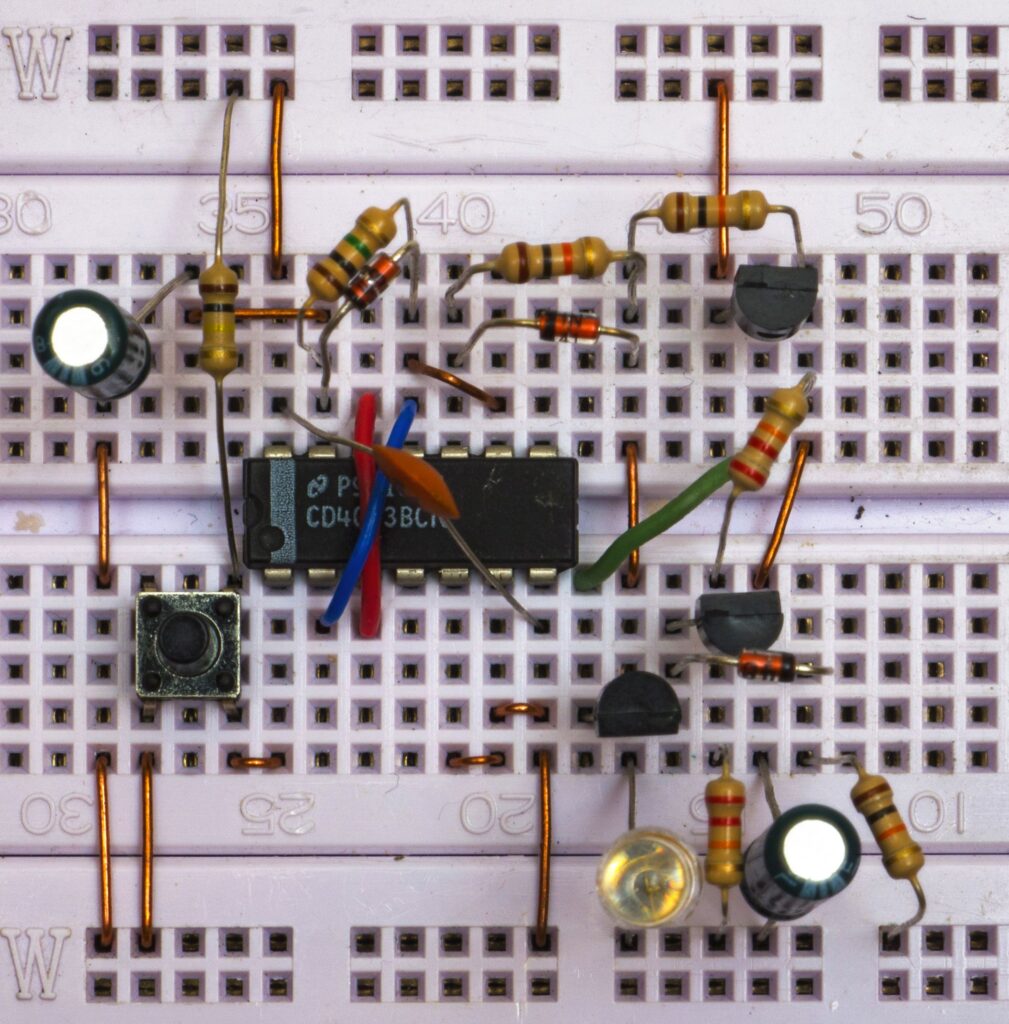

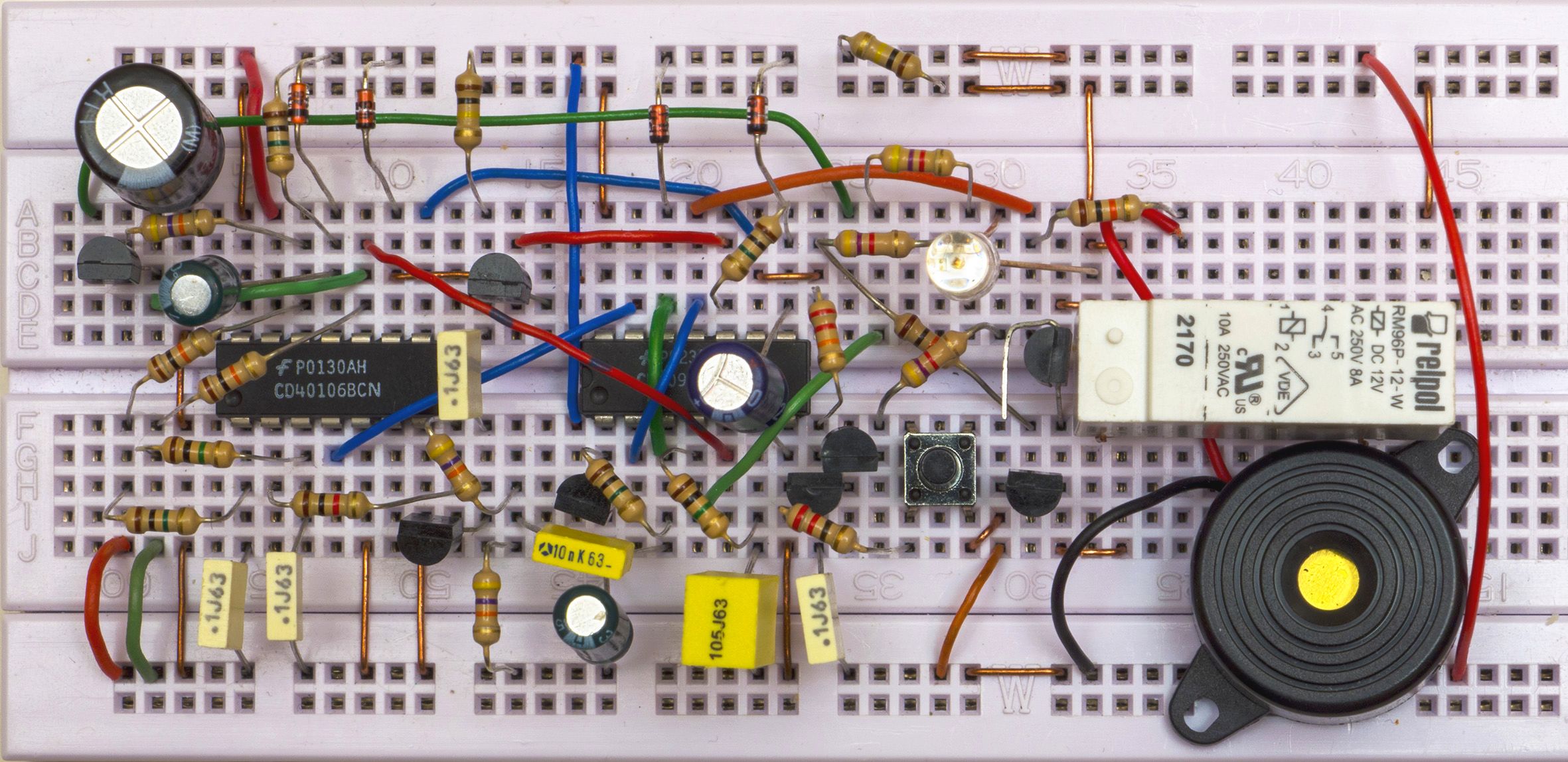

Prostą, ale w pełni użyteczną centralkę alarmową możesz zrealizować według rysunku A i fotografii tytułowej.

Uwaga! Jak podane jest u góry schematu, diody D5, D6, D7 to złącza kolektor-baza tranzystorów PNP typu BC558, o czym przypominają niebieskie literki C, B.

Centralki alarmowe standardowo zasilane są z akumulatora napięciem 12 V, które cały czas podane jest na punkty P, M. Użytkownik obsługuje centralkę za pomocą przełącznika S2, dobrze ukrytego wewnątrz chronionego pomieszczenia. Gdy punkt S jest dołączony do plusa zasilania, centralka jest wyłączona i nie pobiera prądu. Zwarcie punktu S do masy rozpoczyna pracę. Stan centralki sygnalizuje trzykolorowa dioda LED.

Centralka ma dwie linie dozorowe L1 i L2. W liniach tych w stanie czuwania płynie niewielki prąd (ok. 1,2 mA). Natychmiast wywoła alarm przerwanie linii L1, w której są szeregowo połączone np. czujniki otwarcia okien, czujniki zbicia szyby, pasywne czujki podczerwieni (PIR) lub tzw. czujki dualne. Włącza się wtedy przekaźnik uruchamiający syrenę i ewentualne zdalne powiadomienie.

Natomiast linia zwłoczna L2 chroni tylko drzwi wejściowe. Jej przerwanie włączy brzęczyk, ale właściwy alarm wywoła dopiero po czasie opóźnienia (około 10 sekund). Po otwarciu drzwi właściciel ma tyle czasu, by wyłączyć alarm wyłącznikiem S2 ukrytym w sobie wiadomym miejscu. Przypomina mu o tym dźwięk brzęczyka. Linia zwłoczna L2 jest zupełnie nieaktywna przez około 10 sekund po włączeniu centralki przełącznikiem S1, co umożliwi właścicielowi wyjście i zamknięcie drzwi. W tym czasie świeci zielona struktura diody LED, a gdy centralka czuwa, niebieska struktura sygnalizuje to migotaniem.

Centralka ma dodatkowo układ pamięciowy, który zapamiętuje fakt wystąpienia alarmu i sygnalizuje to świeceniem czerwonej struktury. Przycisk S1 służy do kasowania pamięci alarmu.

Alarm działa w powszechnie przyjęty sposób: nawet krótkie naruszenie głównej linii L1 powoduje wywołanie alarmu na czas około dwóch minut; na taki sam czas włączy alarm trwałe przerwanie linii (by w razie jakiejś awarii alarm nie wył długo ku utrapieniu sąsiadów).

Opis układu dla „zaawansowanych”

Centralka ma być cały czas pod napięciem. Gdy punkt S jest dołączony do plusa zasilania (SPOCZYNEK) wtedy wszystkie kondensatory elektrolityczne są naładowane, co zapewnia ich niezawodną pracę. W punktach A, B napięcie jest równe zeru i obie linie L1, L2 są nieczynne. W punktach C, D, E, F jest stan wysoki, a w punkcie G – niski.

Po zwarciu punktu S do masy (PRACA) od razu pojawia się napięcie zasilające w punkcie A i linia L1 jest gotowa do pracy i może natychmiast wywołać alarm.

Zaświeca się zielona kontrolka sterowana przez T3. Kondensator C7 zaczyna się pomału rozładowywać przez R10, przez co stan wysoki w punkcie B pojawi się około 10 sekund po włączeniu alarmu. Zgaśnie zielona lampka i zacznie pulsować kontrolka niebieska, sterowana przez generator U2D, sygnalizująca czuwanie centralki.

Nawet krótkie (ale powyżej 50 ms) przerwanie linii L1 spowoduje pojawienie się stanu niskiego w punkcie C, a dzięki kondensatorowi C5 na chwilę także w punkcie F. Zmieni to stan przerzutnika RS na bramkach U1D, U2C, który wraz z R8, C6 jest głównym układem czasowym alarmu – w punkcie G pojawi się stan wysoki, co włączy przekaźnik REL. Włączy też strukturę tyrystorową T4, T5, zaświecając trwale czerwoną kontrolkę pamięci alarmu (którą można zgasić, naciskając S1).

Kondensator C6 będzie się pomału rozładowywał przez R8, co po około 100 sekundach wyłączy alarm.

Natomiast przerwanie linii zwłocznej L2 wywoła stan niski w punkcie D, co przełączy przerzutnik zbudowany z U2A, U2D. Odezwie się brzęczyk Y1 i w punkcie E pojawi się stan niski, przez co C3 zacznie się rozładowywać przez R3. Po około 10 sekundach przerzutnik powróci do stanu spoczynkowego, czyli w punkcie E pojawi się znów stan wysoki. Dzięki obwodowi C4, R4 na chwilę otworzy to tranzystor T1, który włączy układ czasowy alarmu (U1D, U2C).

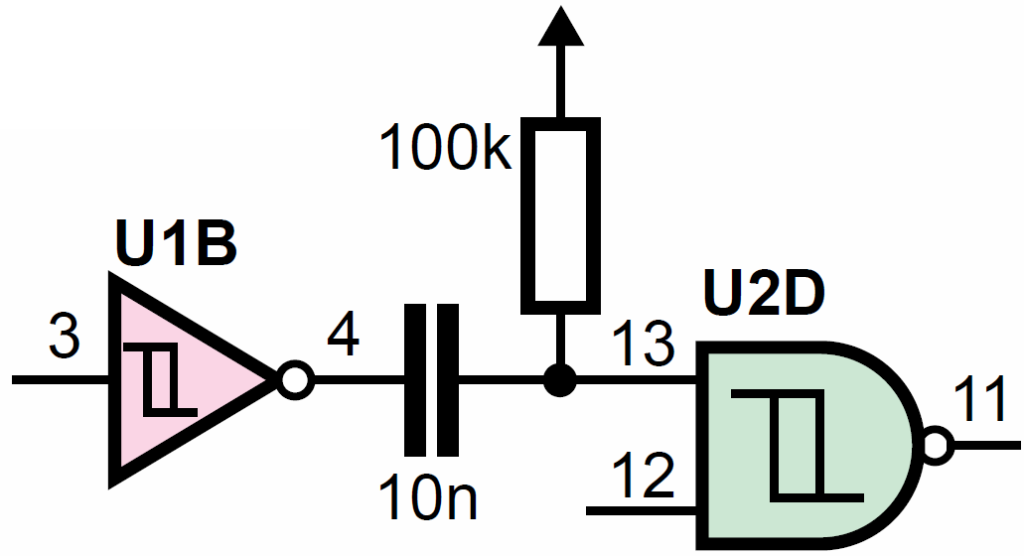

W takiej konfiguracji trwałe przerwanie linii zwłocznej L2, chroniącej zazwyczaj tylko drzwi wejściowe, spowoduje pracę bramki U2A jako generatora i syrena alarmowa będzie włączona niemal bez przerwy. Aby trwałe przerwanie linii L2, na przykład wskutek jakiejś awarii, spowodowało tylko jednokrotny alarm, wystarczy pomiędzy bramki U1B, U2D włączyć obwód RC według rysunku B.

Oczywiście można według potrzeb modyfikować czasy alarmu (R8, C6), czasu na wejście (R3, C3) oraz czasu na wyjście (R10, C7), stosując kondensatory w zakresie 100 uF…1000 uF i rezystory 100 kΩ..1 MΩ.

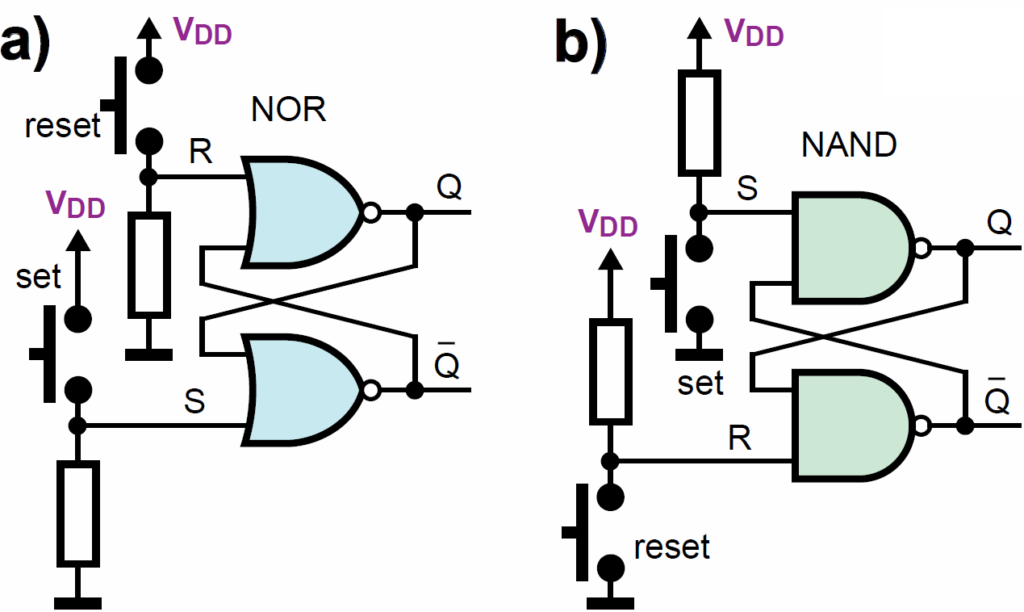

Poznajemy elementy i układy elektroniczne

W tym wykładzie zajmiemy się bliżej przerzutnikami. Już wcześniej, w wykładzie 3 realizowaliśmy najprostsze dwustanowe przerzutniki RS (reset/set – wyłącz/załącz). Choć w podręcznikach działanie przerzutników opisuje się w różny sposób, m.in. za pomocą tabeli i grafów, my chcemy podejść do zagadnienia jak najprościej i od strony jak najbardziej praktycznej. Dlatego możemy rozumieć, że wejścia takich przerzutników RS mają stany spoczynkowe i stany aktywne. Dla przerzutnika RS z bramek NOR z rysunku 1a stanem spoczynkowym wejść jest stan niski L, czyli zero logiczne (0). Stan wyjść możemy zmieniać podając na wejścia stan aktywny – w tym przypadku wysoki (H), czyli jedynkę logiczną. Dla przerzutnika z bramek NAND z rysunku 1b stanem spoczynkowym wejść jest stan wysoki, a stan wyjść możemy zmieniać podając na wejścia stan niski. Przerzutniki mają dwa wyjścia: proste Q i zanegowane (Q\) .

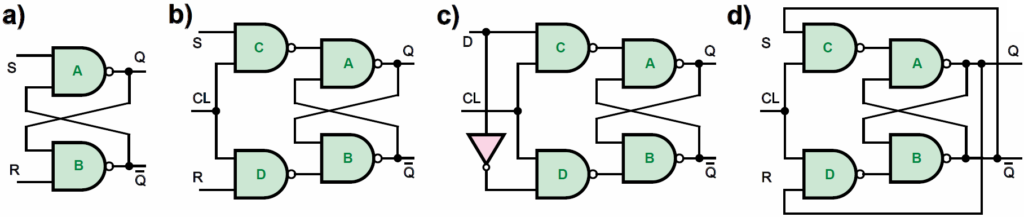

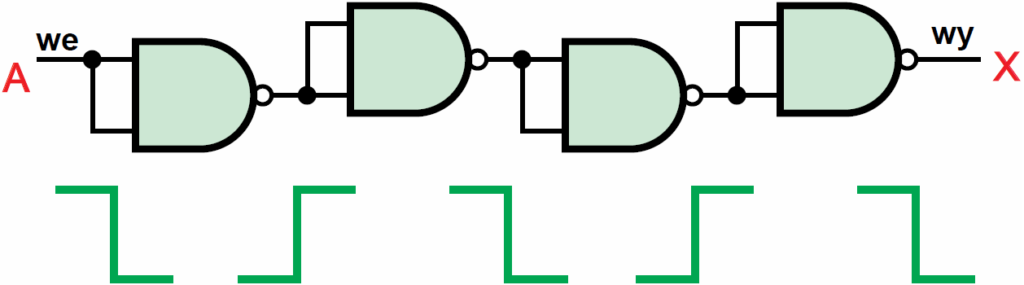

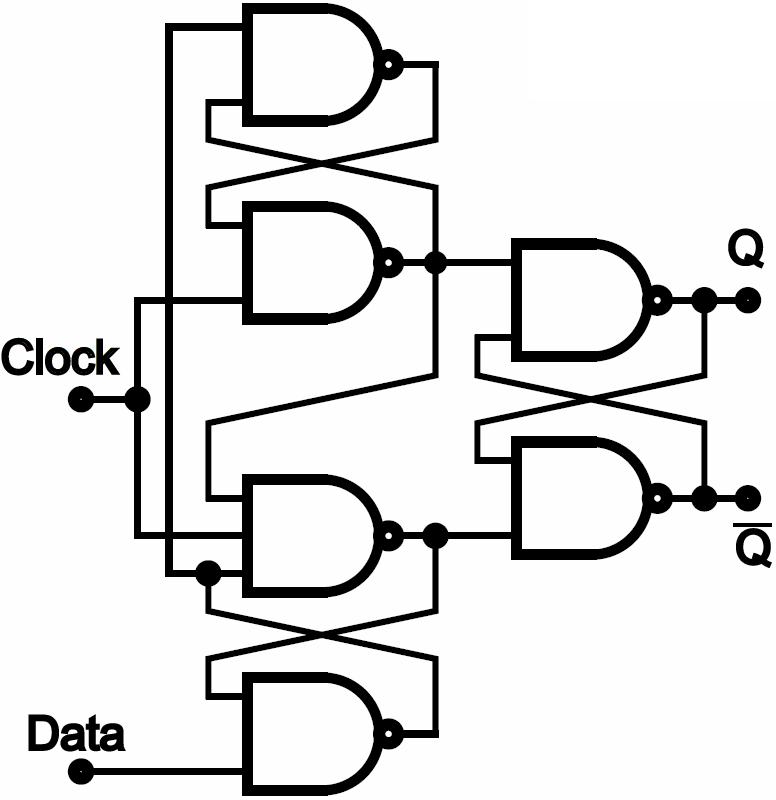

Takie przerzutniki RS nazywamy asynchronicznymi, ponieważ stan ich wyjść może zmienić się w dowolnej chwili, tuż po pojawieniu się stanu aktywnego na wejściach. W praktyce okazało się, że jeszcze bardziej pożyteczne są tzw. przerzutniki synchroniczne, w których stany wyjść mogą zmieniać się tylko w ściśle określonych momentach, wyznaczonych przez tak zwany sygnał zegarowy (przebieg taktujący). Na rysunku 2 pokazany jest bodaj najprostszy asynchroniczny przerzutnik RS. Dodanie dwóch bramek na wejściach według rysunku 2b daje przerzutnik RS z dodatkowym wejściem zegarowym CL (albo CP), gdzie zmiany stanów mogą następować tylko w obecności (dodatniego) impulsu zegarowego. Literki CL (CP) na wejściu zegarowym pochodzą od angielskiego clock – zegar. Tylko w obecności poziomu (stanu) wysokiego na wejściu zegarowym CL, bramki przepuszczą dalej dodatnie impulsy z wejść S, R. Dodanie inwertera według rysunku 2c daje przerzutnik z pojedynczym wejściem, oznaczonym D (ang. Data – dane). Także i tutaj stan wyjść może zmieniać się wyłącznie podczas trwania (dodatniego) impulsu zegarowego. Natomiast gdy na wejściu CL panuje stan niski, stan wyjść przerzutnika nie może się zmienić – uzyskaliśmy przerzutnik D-latch (zatrzask), który czasem znajduje praktyczne zastosowanie.

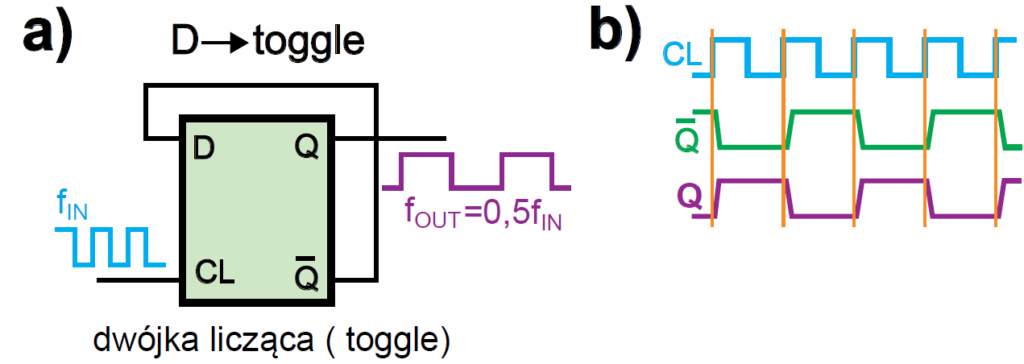

Interesująca jest też konfiguracja z rysunku 2d, gdzie mamy dodatkowe sprzężenie z wyjść na wejścia. Jest o bardzo prymitywna wersja tak zwanego przerzutnika toggle (przeskakujący, przełączający), zwanego dwójką liczącą, gdzie każdy impuls na wejściu zegarowym CL (Clock) powoduje zmianę stanu wyjścia na przeciwny.

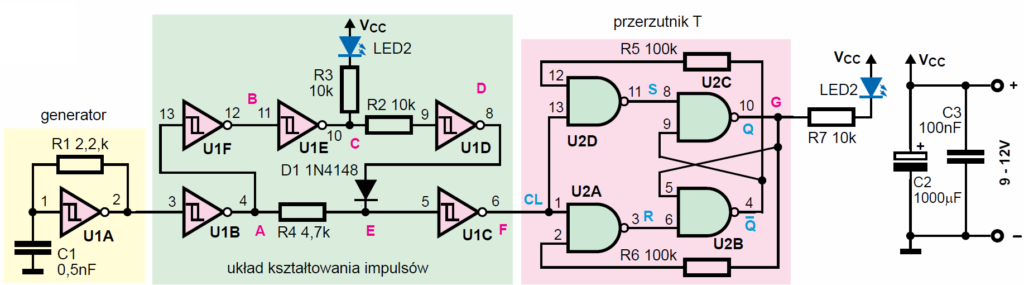

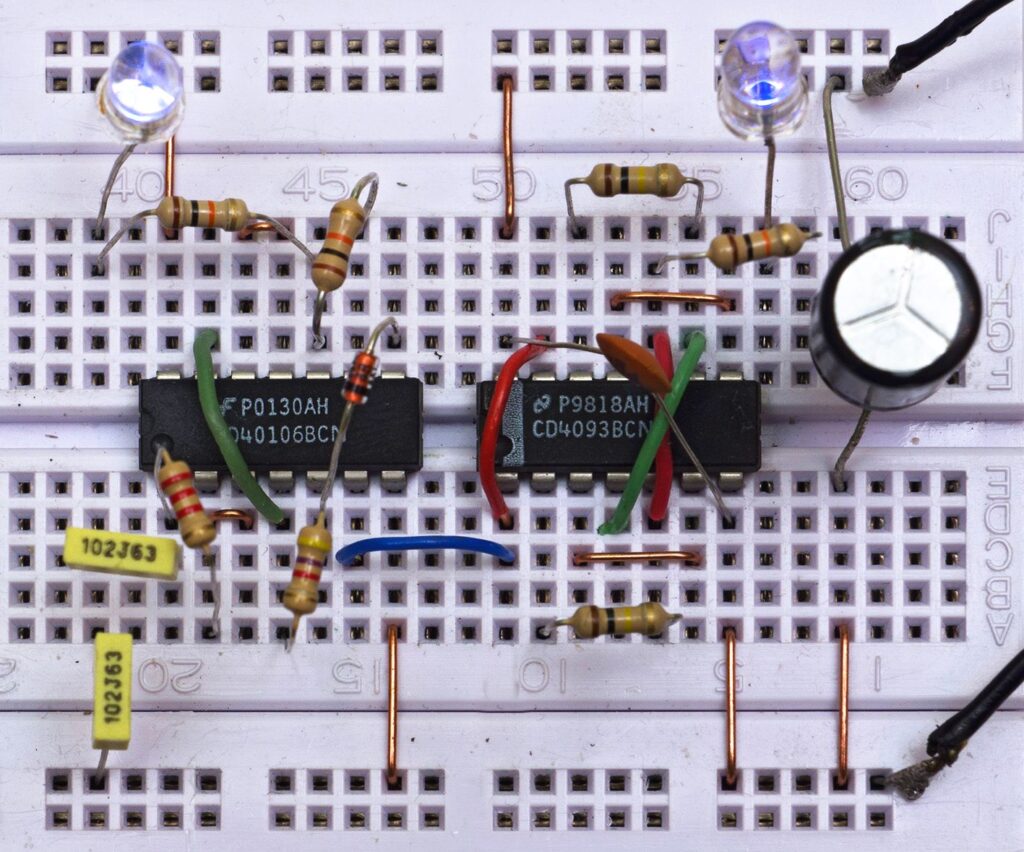

Zbadajmy teraz taki przerzutnik w układzie z rysunku 3 i fotografii 4.

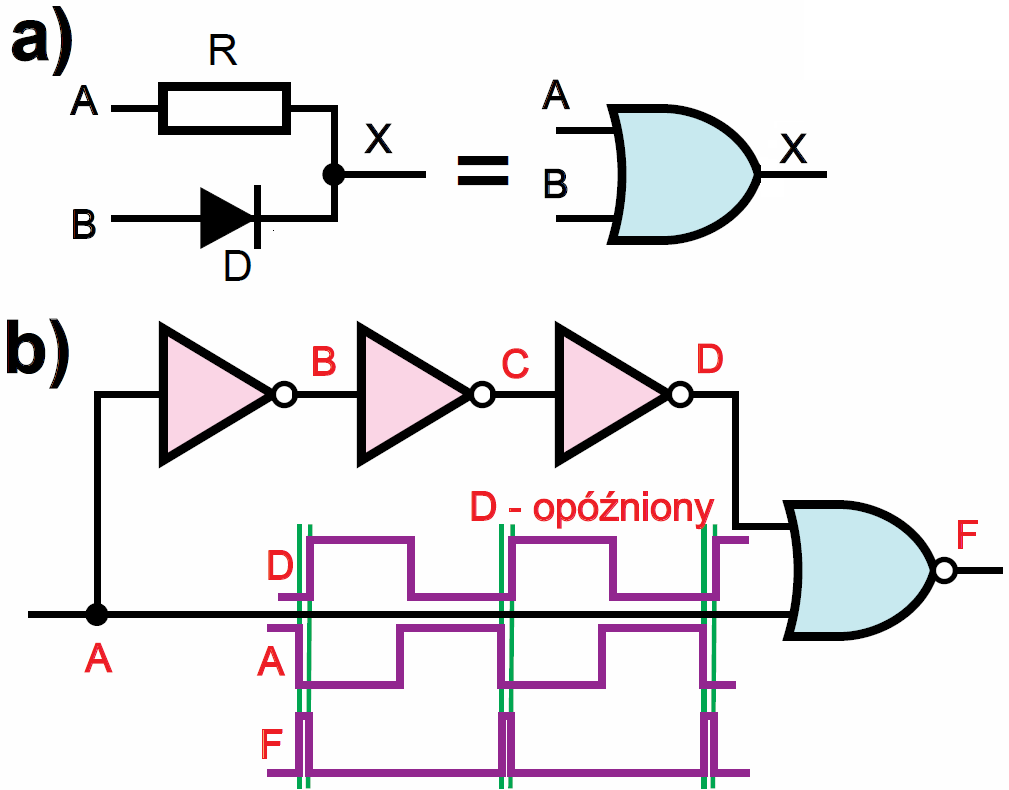

Oprócz przerzutnika zbudowanego na układzie U2 według rysunku 2d mamy prosty generator z inwerterem U1A, obwód formowania impulsów z inwerterami U1C…U1F oraz monitor impulsów z rezystorami R3, R7 i dwiema niebieskimi diodami LED. Aby uzyskać możliwie dużą częstotliwość pracy, rezystancja R1 jest mała (2,2 kΩ), a pojemność C1 wynosi 0,5 nF i jest uzyskana przez szeregowe połączenie dwóch kondensatorów 1 nF. Dziwny obwód z rezystorem R4 i diodą D1 jest rodzajem bramki OR, jak pokazuje rysunek 5a. Układ kształtowania impulsów jest więc odpowiednikiem układu z rysunku 5b.

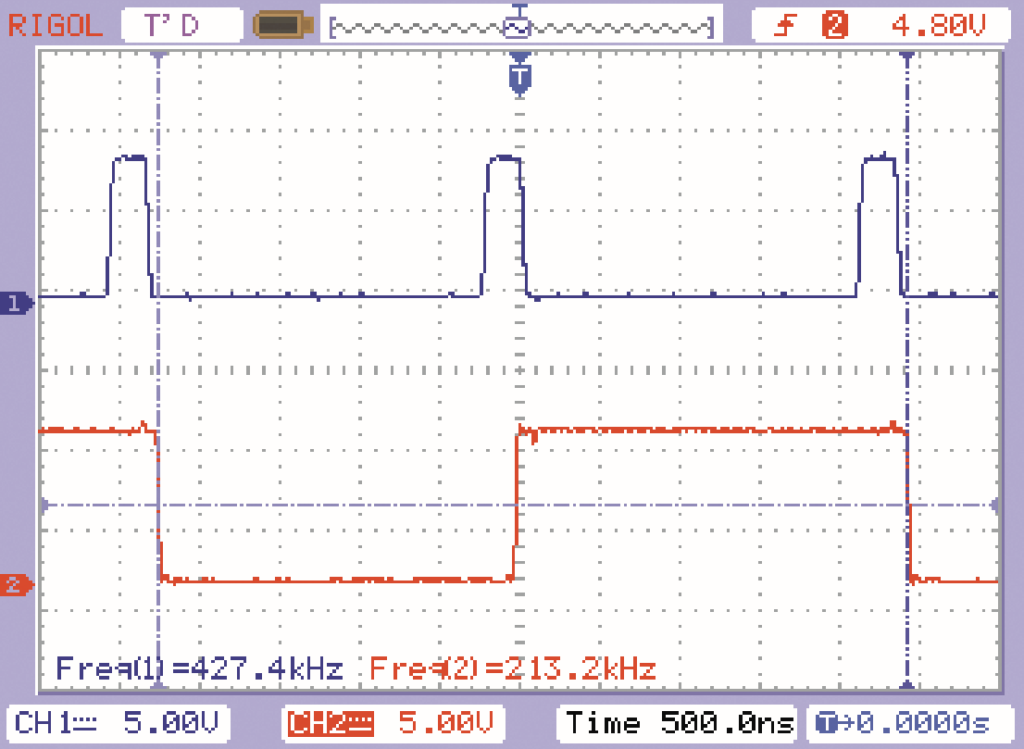

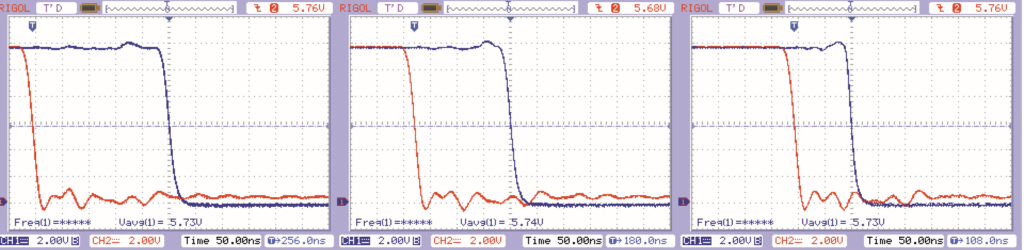

Rezystor R2 wraz z pojemnością wejściową inwertera U1D tworzy układ opóźniający RC i dodatkowo wydłuża czas impulsu. Rysunek 6, zrzut z ekranu oscyloskopu, pokazuje przebiegi w punktach F, G układu z rysunku 3, gdzie częstotliwość pracy generatora wynosi ponad 400 kHz, a impulsy zegarowe w punkcie F (CL) mają długość nieco ponad 200 ns. Każdy impuls na wejściu zegarowym CL powoduje zmianę stanu przerzutnika, a więc przerzutnik ten dzieli częstotliwość przez dwa (jest tzw. dwójką liczącą), co zresztą jest wprost podane na ekranie oscyloskopu.

Bez głębszej analizy można łatwo zauważyć, że dwójka licząca z rysunku 3 zawiera w sobie przerzutnik RS (U2B, U2C) i że każdy krótki impuls podawany na wejście zegarowe (CL) przerzutnika T przejdzie tylko przez jedną z bramek U2A lub U2D albo na wejście R, albo na wejście S – przez tę bramkę, na której drugim wejściu panuje stan wysoki. Połączenia są tak dobrane, że zmienia to stan przerzutnika na przeciwny. Otrzymaliśmy działający dzielnik częstotliwości przez 2, ale o tyle niedoskonały, że musi być on sterowany krótkimi dodatnimi impulsami zegarowymi o ściśle dobranym czasie trwania. Gdyby czas trwania impulsów zegarowych był krótszy lub dłuższy, przerzutnik ten nie będzie prawidłowo pracował.

Aby prawidłowo pracowały egzemplarze układu U2 o różnych czasach propagacji, dodany jest nie tylko rezystor R2, wydłużający impulsy zegarowe, ale też dwa rezystory R5, R6 (100 kΩ), które z pojemnościami współpracujących wejść tworzą układy opóźniające. Opóźnienie wprowadzane przez R5, R6 pozwala przerzutnikowi pracować przy nieco dłuższych impulsach zegarowych.

Szczegółowa analiza problemu opóźnień i długości impulsów byłaby zbyt zawiła i zdecydowanie wykraczałaby poza ramy kursu PKE. Najbardziej dociekliwi Czytelnicy mogą przeanalizować zagadnienie samodzielnie lub poszukać w literaturze, a jeśli posiadają oscyloskop – obejrzeć występujące przebiegi. W każdym razie kluczowe znaczenie w pracy tego i innych przerzutników mają maleńkie opóźnienia, wprowadzane przez tworzące go bramki.

Problem jest o tyle ważny, że bardzo często te maleńkie opóźnienia decydują o prawidłowej bądź nieprawidłowej pracy układów cyfrowych. Dlatego musimy poznać choć zarys tego ważnego zagadnienia.

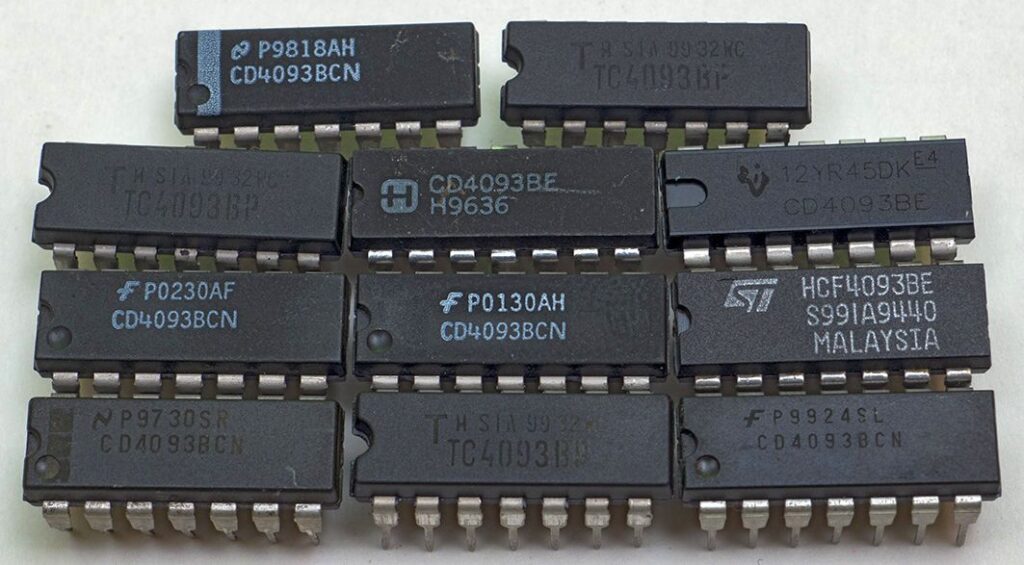

W zasadzie tranzystory MOSFET, tworzące układy CMOS mogłyby być niemal nieskończenie szybkie, bowiem tranzystory te (w przeciwieństwie do bipolarnych) bez opóźnienia reagują na zmiany napięcia bramki. Teoretycznie tranzystor MOSFET mógłby mieć czas włączenia i wyłączenia rzędu 0,1…0,3 nanosekundy, czyli poniżej miliardowej części sekundy. Tak, tylko w praktyce problem wynika z konieczności przeładowania pojemności bramek wszystkich tranzystorów składowych przez wewnętrzne tranzystory, które mają niedużą wydajność prądową. Przygotowując to ćwiczenie, połączyłem wszystkie cztery bramki kostki 4093 w szereg według rysunku 7 zbadałem ich pracę ze wszystkimi posiadanymi egzemplarzami układu 4093 – fotografia 8.

Zbadałem przebiegi w punktach A, X (obserwowałem opadające zbocza) i zmierzyłem czasy propagacji, czyli opóźnienia. Rysunek 9, zrzut z ekranu oscyloskopu, pokazuje czerwone wejściowe przebiegi w punkcie A i opóźnione niebieskie przebiegi wyjściowe w punkcie X trzech moich kostek 4093, o największym, średnim i najkrótszym czasie propagacji (przy napięciu zasilania 12 V). Jak widać, posiadane przeze mnie egzemplarze mają czasy propagacji przez 4 bramki w zakresie 108 … 256 nanosekund, czyli posiadane przeze mnie pojedyncze bramki mają opóźnienie rzędu 27…64 nanosekund. Nic dziwnego, że najwolniejsze egzemplarze nie chciały pracować przy impulsach zegarowych o czasie trwania 100 ns (bez rezystora R2), bo w nich czas propagacji przez dwie bramki jest większy (128 ns), więc przerzutnik nie zdążył się zatrzasnąć.

Podkreślam, że podane właśnie czasy dotyczą napięcia zasilania 12 V. Przy niższym napięciu czasy propagacji są znacznie dłuższe. Na przykład przy napięciu zasilania 12 V mój układ formowania impulsów z rysunku 3 dawał impuls o czasie trwania około 160 ns, przy zasilaniu 9 V około 220 ns, natomiast przy 5 V – ponad 600 ns. W każdym razie mój model z najszybszą posiadaną kostką kostką U2 pracował prawidłowo w zakresie napięć zasilania 4,6 V do 15 V, natomiast z kostką U2 najwolniejszą, już przy zasilaniu powyżej 3,9 V.

W ramach elementarnego kursu PKE nie sposób przeanalizować wszystkich szczegółów. Ale trzeba podkreślić, że omawiane opóźnienia w niektórych układach są dobrodziejstwem, a w innych przekleństwem. Miedzy innymi opóźnienia ograniczają maksymalną częstotliwość pracy w bardziej skomplikowanych systemach.

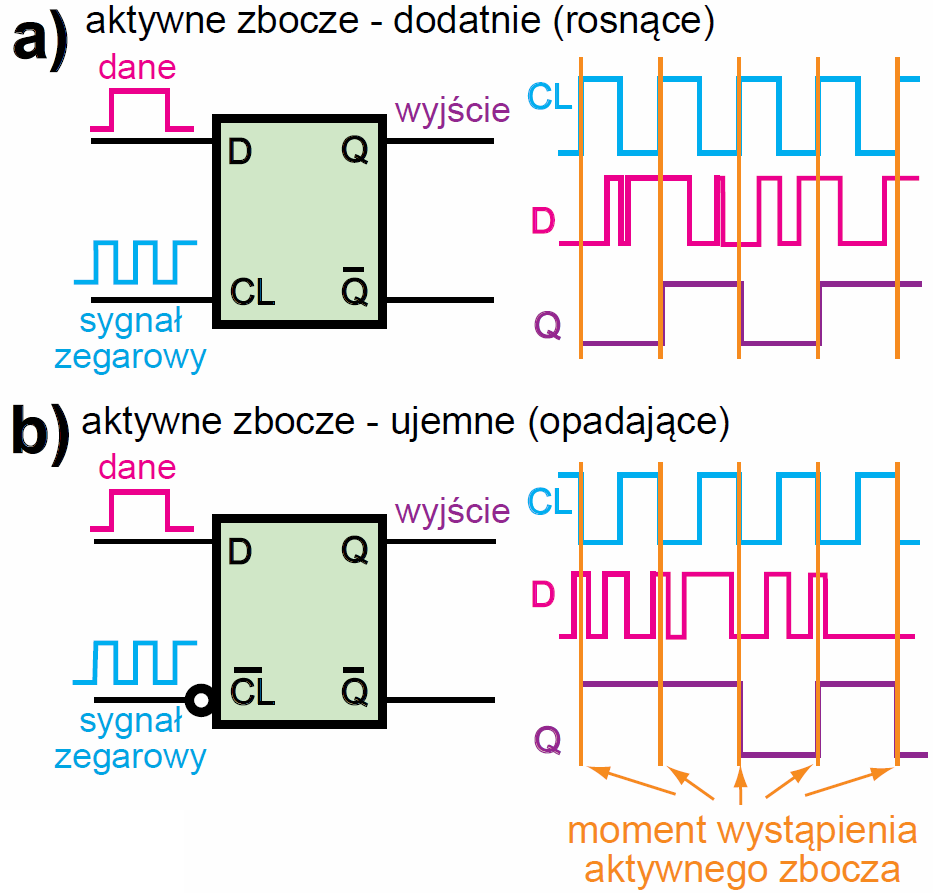

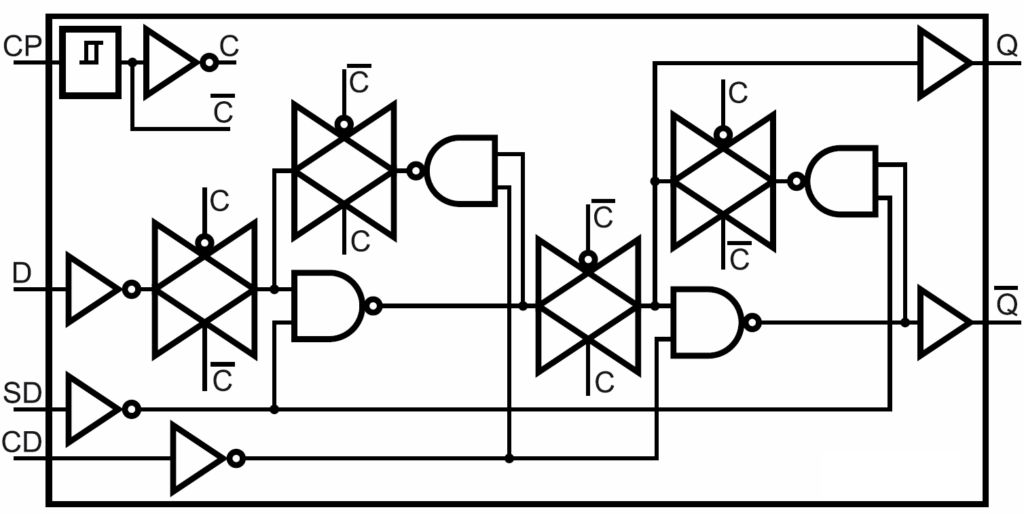

Wracajmy do przerzutników. Aby prawidłowo pracował prosty przerzutnik toggle według rysunku 2d i 3, długość impulsów zegarowych trzeba byłoby indywidualnie dobierać do każdego egzemplarza, stosownie do czasów propagacji tworzących do bramek. Tymczasem w praktyce bardzo przydatne okazują się takie przerzutniki, których działanie nie jest zależne od czasu trwania impulsów zegarowych, które reagują nie tyle na cały impuls, tylko na jedno jego zbocze (rosnące lub opadające). W naszym Praktycznym Kursie Elektroniki nie możemy sobie pozwolić na obszerną analizę tego skądinąd bardzo ważnego, ale i obszernego zagadnienia. Informacje na ten temat znajdziesz w podręcznikach i w Internecie. My pominiemy szczegółowe rozważania (o przerzutnikach wyzwalanych poziomem i zboczem, o dwuzboczowych przerzutnikach Master-Slave, itp.) i powiemy tylko, że opracowano bardziej rozbudowane przerzutniki, których stan może zmienić się wyłącznie pod wpływem i w chwili występowania zbocza sygnału zegarowego. Przykładem może być tak zwany przerzutnik D o schemacie pokazanym na rysunku 10. Szczegółowa analiza nie jest potrzebna. Ważna jest pełniona funkcja.

Przerzutnik D. Działanie „prawdziwego” przerzutnika D wyzwalanego zboczem (D flip flop) jest dziecinnie proste: każde aktywne zbocze sygnału zegarowego powoduje wpisanie na wyjście Q przerzutnika – stanu, jaki wtedy panuje na wejściu informacyjnym D (ang. data – dane). W przeciwieństwie do prostszego przerzutnika D-latch z rysunku 2c, który jest „przezroczysty” przez cały czas trwania stanu wysokiego na wejściu zegarowym, „prawdziwy” przerzutnik D (D flip-flop) może zmienić swój stan wyłącznie w chwili występowania aktywnego zbocza sygnału zegarowego. Rysunek 11 przedstawia działanie przerzutników D z aktywnym zboczem dodatnim (rosnącym) i ujemnym (opadającym).

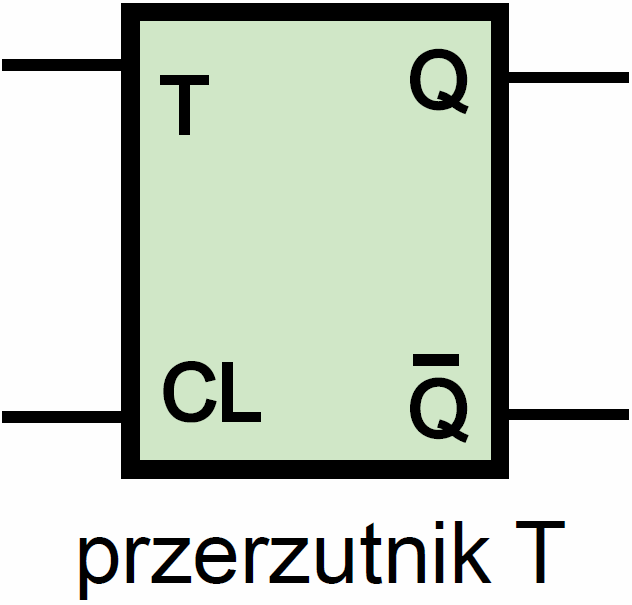

Przerzutnik T ma wejście zegarowe i wejście sterujące T – rysunek 12. Gdy na wejściu T jest stan 0, sygnał zegarowy nie zmienia stanu wyjść. Nas interesuje to, że gdy na wejściu T jest stan wysoki (1), każde aktywne zbocze sygnału zegarowego powoduje zmianę stanów wyjść na przeciwne.

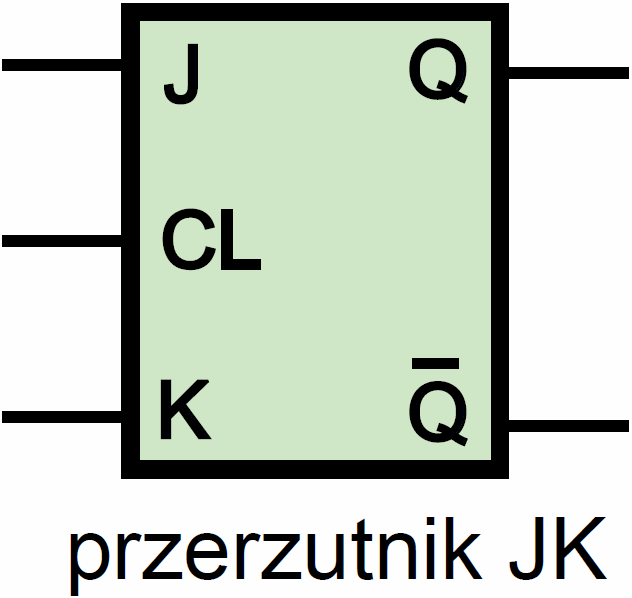

Przerzutnik JK ma dwa wejścia informacyjne (rysunek 13) i jest bardziej uniwersalny. Stan wyjść Q, Q\ można zmienić podczas aktywnego zbocza sygnału zegarowego zależnie od stanu wejść informacyjnych J, K:

gdy J=0, K=0: stan wyjść Q, Q\ nie zmienia się,

gdy J=0, K=1: ustawia Q=0, Q\=1,

gdy J=1, K=0: ustawia Q=1, Q\=0,

gdy J=1, K=1: stany wyjść Q, Q\ zmieniają się na przeciwne.

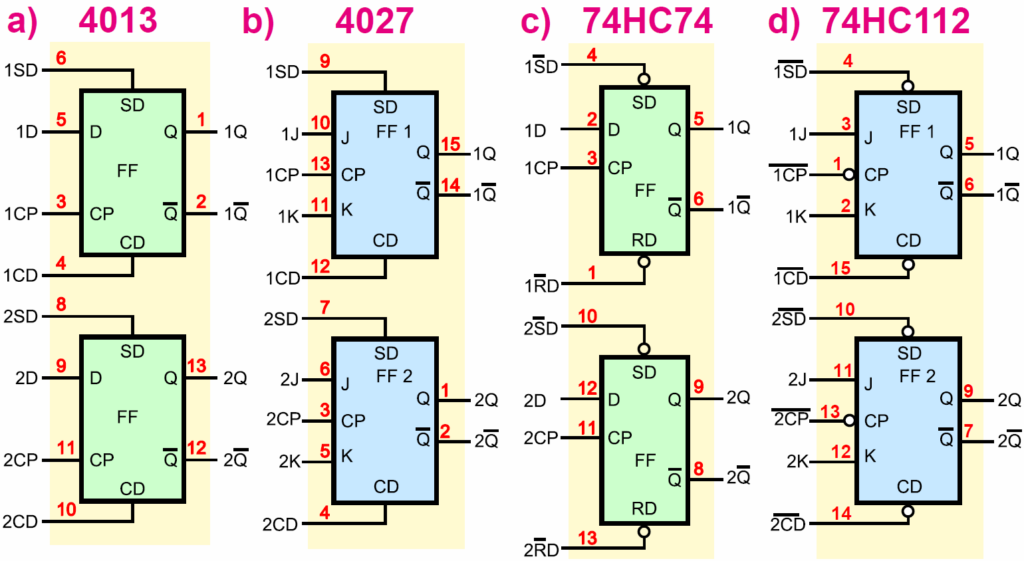

Przerzutniki D oraz JK dostępne są w postaci układów scalonych – patrz rysunek 14. Czerwone napisy to numery nóżek. W rodzinie CMOS 4000 są układy 4013 i 4027, zawierające po dwa przerzutniki D i JK. W rodzinie 74 mamy między innymi 74HC74 oraz 74HC112. Oprócz wejścia zegarowego CP i wejść informacyjnych D lub J, K, każdy z przerzutników ma też asynchroniczne wejścia: zerujące, oznaczone CD lub RD (clear, reset) oraz ustawiające SD (set), pozwalające zmienić stan wyjść w dowolnym momencie. W literaturze spotyka się różne symbole graficzne przerzutników. Na rysunkach 11 i 14 kółeczko na wejściu zegarowym wskazuje, że zboczem aktywnym jest zbocze ujemne – opadające (w 74HC112). W pozostałych aktywne jest zbocze dodatnie – rosnące. Natomiast kółeczko przy wejściu asynchronicznym informuje, że stanem aktywnym jest poziom niski, czyli zero logiczne (wejścia SD, CD, RD).

Na rysunku 14 nie ma żadnej informacji o końcówkach zasilania. W ogromnej większości układów cyfrowych do zasilania służą końcówki „skrajne”. Plus zasilania dołącza się do nóżki o najwyższym numerze (14 lub 16) a minus (masa) to końcówka 7 lub 8.

Warto zapamiętać, że przerzutnik D łatwo jest zmienić w przerzutnik toggle (przeskakujący, w dwójkę liczącą), jak ilustruje rysunek 15a. Gdyby czasy opóźnienia (propagacji) były zerowe, trudno byłoby określić jego działanie. Ale dzięki nanosekundowym opóźnieniom między wejściem D, a wyjściami Q, Q\, działanie jest jednoznaczne. W praktyce przerzutnik D wyzwalany zboczem zawiera dużo więcej bramek, niż te z rysunku 10, więc zmiana stanu wyjść nie nastąpi natychmiast. Aktywne zbocze sygnału zegarowego wpisuje do przerzutnika aktualny stan z wyjścia Q\ (zanegowanego), jak pokazuje to rysunek 15b. „Nowy” stan pojawi się na wyjściach z pewnym niewielkim opóźnieniem (nanosekundy), można powiedzieć, że pojawi się wtedy, gdy aktywne zbocze się już zakończy.

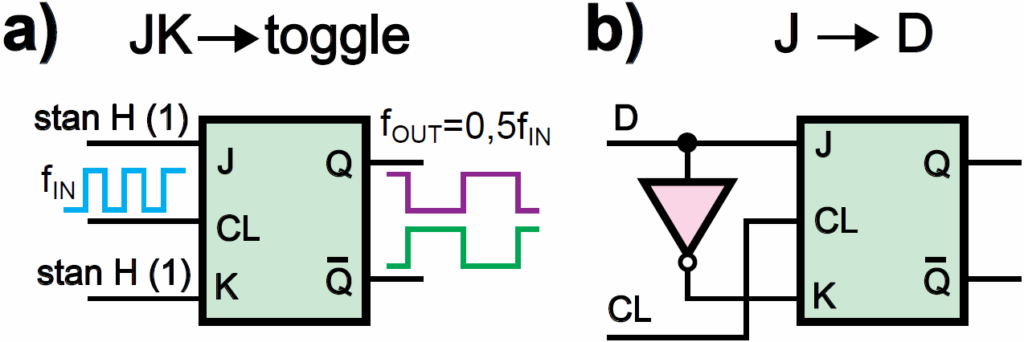

Także przerzutnik JK można łatwo zmienić w przerzutnik toggle. Wystarczy na oba wejścia JK podać stan wysoki – rysunek 16a. Wtedy też na wyjściach otrzymujemy przebiegi o częstotliwości dwa razy mniejszej od sygnału zegarowego. Rysunek 16b pokazuje zamianę przerzutnika JK na przerzutnik D.

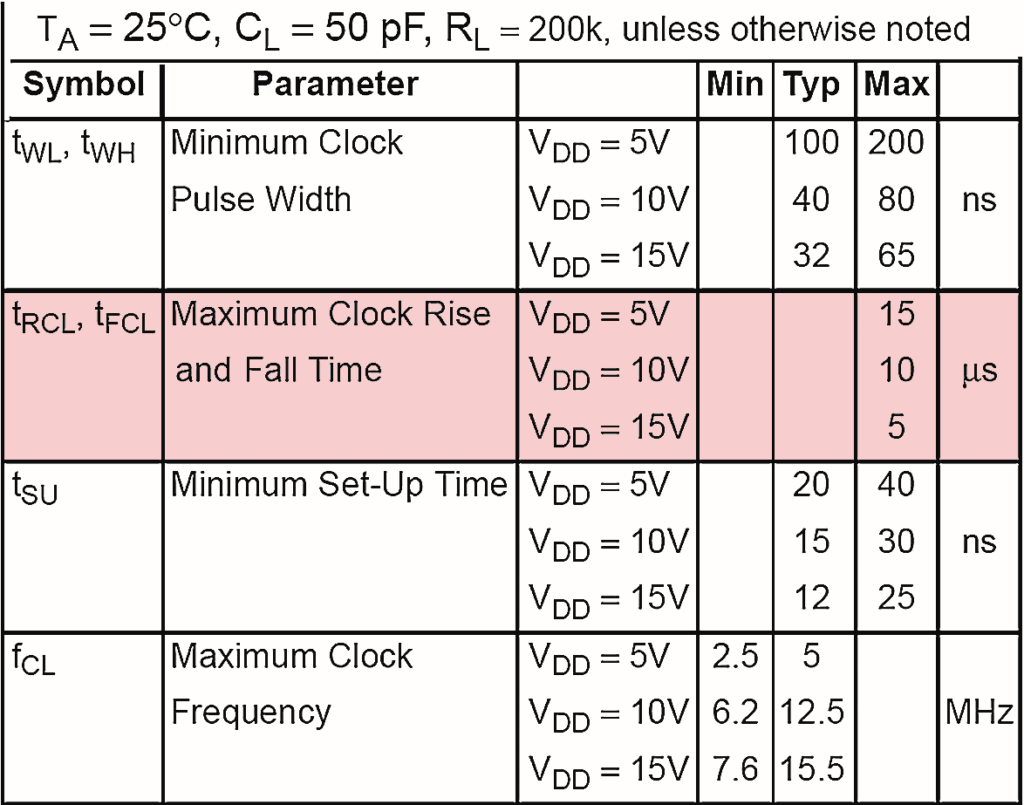

Wróćmy jeszcze do rysunku 15b i odnotujmy kolejny ważny szczegół: otóż czasy opóźnienia między wejściem a wyjściem przerzutnika nie są duże, więc zbocza sygnału zegarowego muszą być odpowiednio strome (czas narastania, opadania musi być krótki). Przy zbyt łagodnych zboczach sygnału zegarowego przerzutniki (a także omówione dalej rejestry i liczniki) mogą działać błędnie.

W katalogach określony jest maksymalny czas narastania i opadania zboczy sygnału zegarowego (Maximum Clock Rise and Fall time). Na przykład dla scalonego przerzutnika D z kostki CMOS 4013 katalog firmy Fairchild podaje informacje zamieszczone na rysunku 17.

Wymagania na stromość zboczy nie ma w katalogu tej kostki produkcji NXP (Philips), ponieważ zgodnie z rysunkiem 18 na wejściu zegarowym CL (CP) kostki HEF4013 jest obwód zapewniający histerezę.

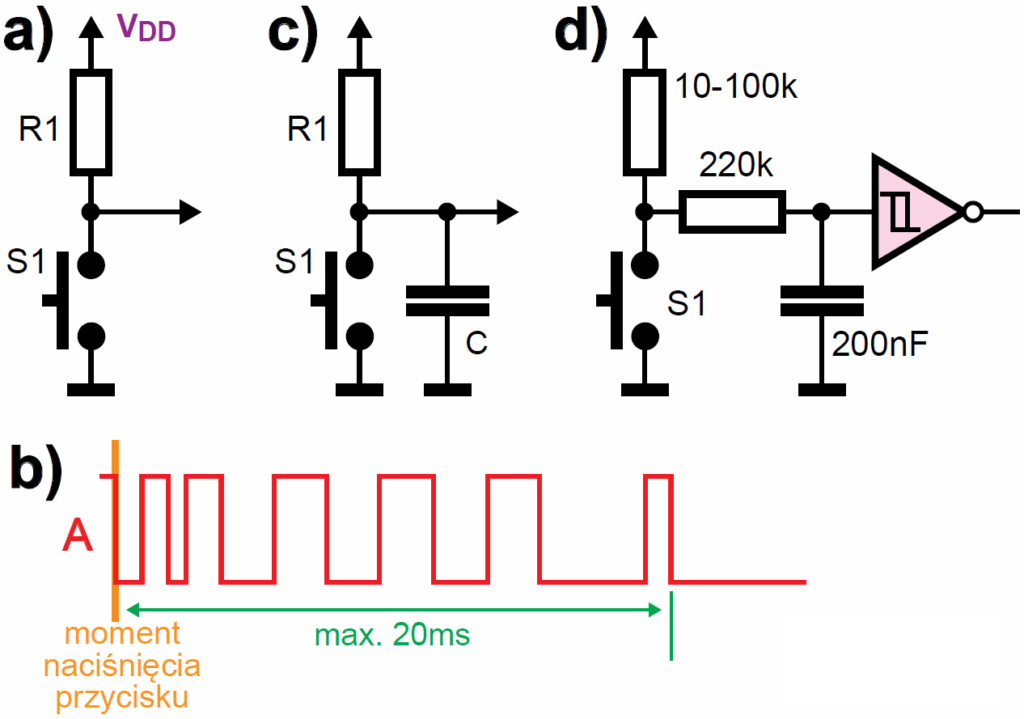

A jeśli zaszliśmy tak daleko, wspomnijmy też o problemie drgań styków, między innymi w przyciskach, które dołączone są do wejść układów cyfrowych – rysunek 19a. Naciśniecie przycisku nie zawsze oznacza jednoznaczną zmianę stanu logicznego. Styki mogą drgać i w efekcie na wejściu może pojawić się seria impulsów o czasie trwania rzędu milisekund (zależnie od rozmiarów styku) – rysunek 19b. Tymczasem układy cyfrowe są bardzo szybkie i takie drgania styku mogą być potraktowane jako „długa” seria impulsów. Proponowane przez niektórych dołączenie kondensatora równolegle do styku według rysunku 19c nie jest zalecanym rozwiązaniem i to przynajmniej z dwóch powodów. Dobrym sposobem jest dodanie obwodu całkującego RC o stałej czasowej nawet do 100 ms i zastosowanie wejścia (Schmitta) z histerezą według rysunku 19d.

Jeszcze jedno istotne zagadnienie. Otóż generalnie nie należy łączyć ze sobą wyjść układów cyfrowych. Gdy wystąpią tam różne stany logiczne, to po pierwsze napięcie wyjściowe nie będzie czystym stanem logicznym, tylko przyjmie jakąś wartość pośrednią. Po drugie, zwiększy to poważnie pobór prądu.

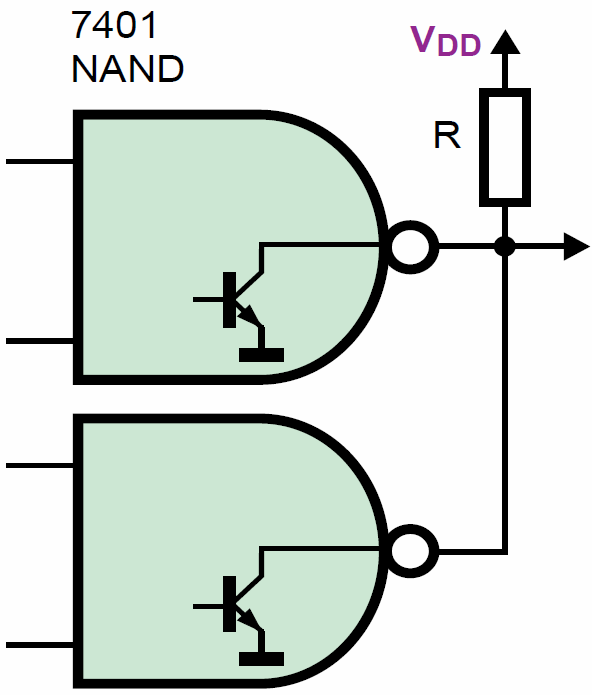

Są jednak wyjątki. Po pierwsze, by zwiększyć wydajność prądową, możemy łączyć równolegle bramki (inwertery), ale tylko z tego samego układu scalonego. Innym wyjątkiem są układy z wyjściem typu otwarty kolektor (OC) Open Collector, spotykane w dawnych układach TTL z tranzystorami bipolarnymi i wyjścia Open Drain w układach CMOS. Rysunek 20 pokazuje takie wykorzystanie bramek NAND z otwartym kolektorem ze starej kostki 7401 (produkowana była też wersja 74HC01 z otwartym drenem). Przy okazji realizujemy funkcję AND „na drucie” (Wire AND). W układach CMOS wyjścia Open Drain nie są praktycznie spotykane.

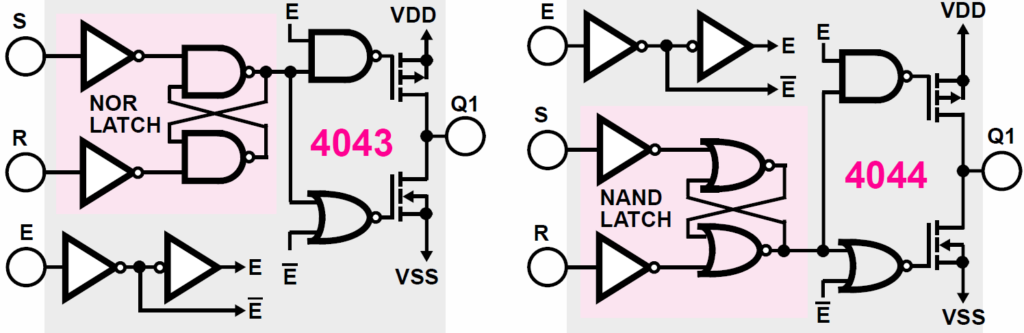

Trzecim wyjątkiem są tzw. wyjścia trójstanowe (tristate outputs) Oprócz stanu niskiego (L) i wysokiego (H) takie wyjście może być wprowadzone w tzw. stan trzeci, stan wysokiej impedancji, gdy oba tranzystory wyjściowe są zatkanie i wyjście jest odcięte, nieczynne, niewidoczne. Układy z wyjściem trójstanowym mają dodatkowe wejście sterujące, oznaczane zwykle E lub OE (Output Enable) – pojawienie się na wejściu OE stanu aktywnego umożliwia pracę wyjścia, a w spoczynku pozostaje ono w stanie trzecim – wyjście jest nieczynne, odcięte. Rysunek 21 pokazuje schematy wewnętrzne przerzutników z kostek CMOS 4043 i 4044 z (pojedynczym) wyjściem trójstanowym. Inne układy rodziny CMOS4000 z takimi wyjściami to na przykład 4076, 4502, 4503, 40245, 40373, 40374. Układy w wyjściami trójstanowymi stosowane są często w różnego rodzaju systemach mikroprocesorowych i komputerowych, gdzie kilka różnych urządzeń współpracuje ze wspólną szyną danych.

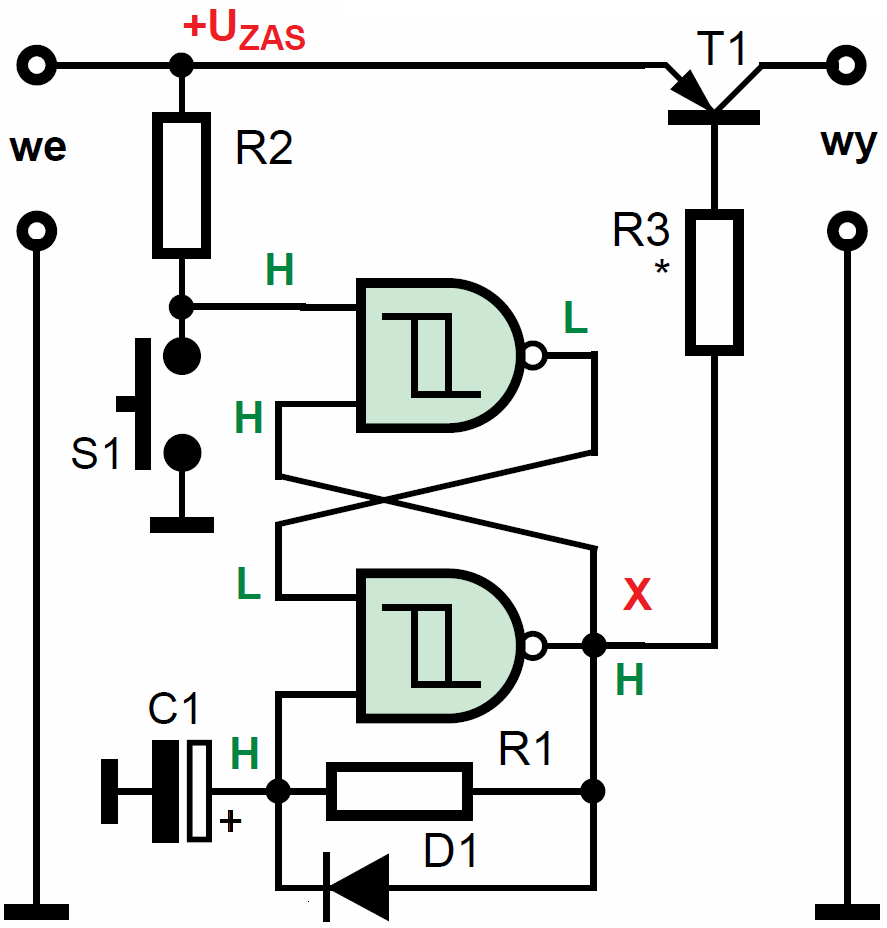

A teraz układy do zrobienia. Rysunek 22 pokazuje prosty wyłącznik czasowy, który może przydać się w urządzeniach zasilanych z baterii do automatycznego wyłączania (AutoPower Off). Zielonym kolorem podane są stany logiczne w spoczynku, gdy T1 jest wyłączony, gdy układ w ogóle nie pobiera prądu. Naciśnięcie S1 zmienia stany wyjściowe przerzutnika, włącza tranzystor T1, a kondensator C1 zaczyna się pomału rozładowywać przez R1. Gdy napięcie na C1 opadnie do progu przełączania, przerzutnik wróci do stanu spoczynku, a kondensator C1 szybko naładuje się przez diodę D1.

Jeszcze bardziej pożyteczna może się okazać wersja z rysunku 23 z prostym stabilizatorem LDO, gdzie napięcie baterii jest obniżane i stabilizowane do poziomu wyznaczonego przez dzielnik R6/R7. Mój model pokazany jest na fotografii 24. Wartości R1 = 1 MΩ i C1 = 10 uF zapewniają czas pracy około 10s.

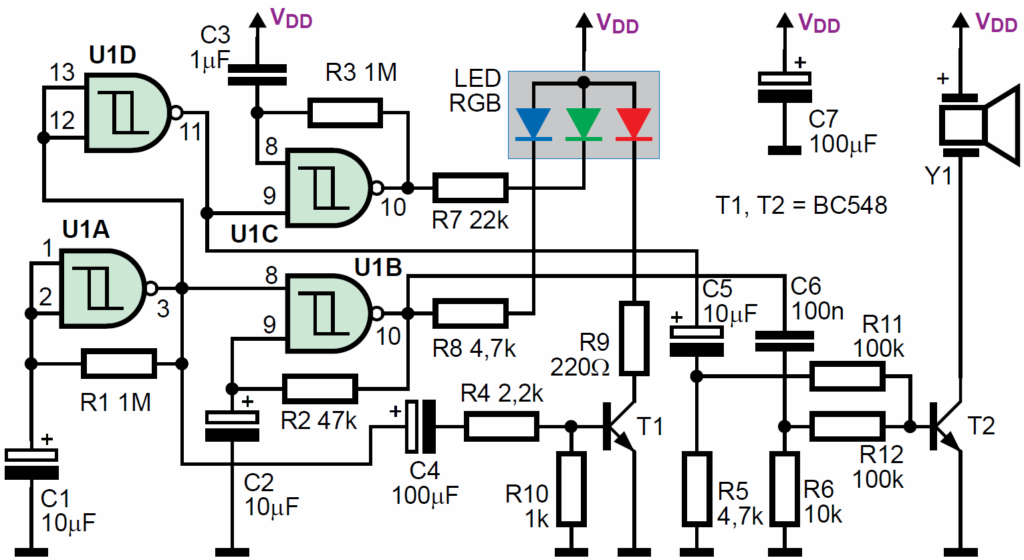

Układ z rysunku 25 i fotografii 26 to zaawansowany symulator alarmu. Nie zawsze trzeba instalować system alarmowy – często wystarczy efekt psychologiczny, zapewniany przez symulator alarmu, ale nie tak prymitywny, jak pojedyncza migająca dioda LED. Proponowany układ zawiera trójkolorową diodę LED RGB, a nieskomplikowany układ sterujący wytwarza intrygującą sekwencję różnokolorowych błysków, udając monitor jakiegoś skomplikowanego systemu. Generator U1A o okresie kilku sekund (R1, C1) na przemian włącza generatory U1B, U1C, sterujące niebieską (R2, C2) i zieloną (R3, C3) strukturą diody LED RGB, co daje serie niebieskich i zielonych impulsów. Wraz z rozpoczęciem niebieskiej serii impulsów na około pół sekundy (C4, R4) silnie zaświeca się struktura czerwona, dając intensywny błysk czerwono-purpurowy. Wraz z błyskaniem niebieskiej struktury brzęczyk Y1 wydaje krótkie (R6, C6) ciche stuknięcia, a na ich zakończenie nieco dłuższy (R5, C5) pisk. Celowo R7, R8 mają znaczną wartość by świecenie zielonej i niebieskiej struktury było znacznie mniej intensywne, niż czerwony błysk (R9).

Masz już sporą wiedzę, dlatego zachęcam żebyś zmodyfikował nie tylko wartości wymienionych elementów, ale też sam układ, by uzyskać inne sekwencje błysków i dźwięków. A my w następnym wykładzie zajmiemy się rejestrami i licznikami.

Piotr Górecki