Pierwsze kroki w cyfrówce – część 13

W poprzednim odcinku zapoznałeś się z przerzutnikami typu RS oraz D. Dziś pora na kolejne.

Przerzutnik typu Latch (zatrzask)

Na pewno spotkałeś się już z określeniem „zatrzask” albo „latch” (czytaj: lacz).

W literaturze można się jednak natknąć na pewne niekonsekwencje w nazewnictwie i oznaczeniach, co początkującym robi w głowie sporo zamieszania.

Spotyka się bowiem określenia: „przerzutnik typu latch wyzwalany zboczem” oraz „przerzutnik typu latch wyzwalany poziomem”, albo też określenia „przerzutnik typu D wyzwalany zboczem” oraz „przerzutnik typu D wyzwalany poziomem”. Przetnijmy wątpliwości.

Pod określeniem: „przerzutnik typu latch wyzwalany zboczem” oraz „przerzutnik typu D wyzwalany zboczem” kryje się po prostu poznany w poprzednim odcinku przerzutnik D (albo zespół kilku takich przerzutników).

Natomiast najczęściej mówiąc „latch” czy „zatrzask” mamy na myśli przerzutnik sterowany poziomem.

Działanie takiego przerzutnika jest trochę podobne do działania przerzutnika D, ale występuje istotna różnica.

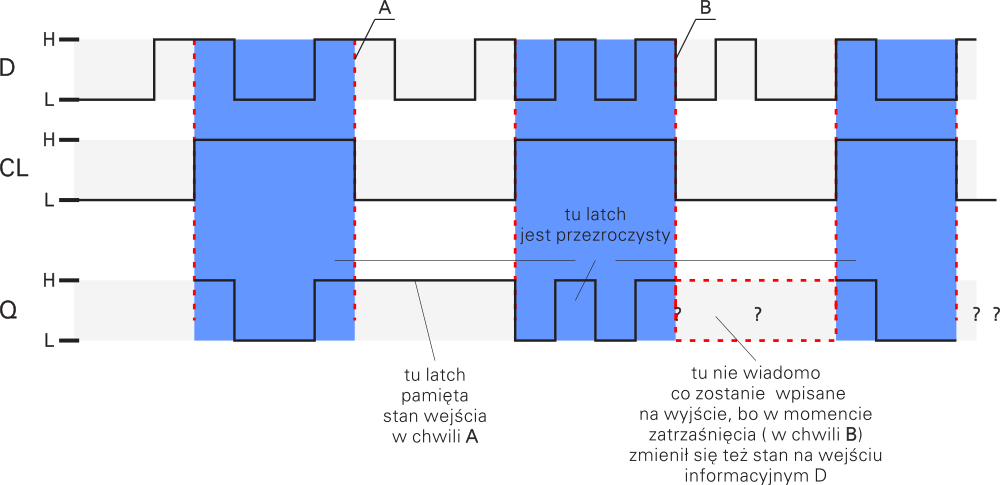

Różnica polega na tym, że przerzutnik D wpisuje na wyjście dane w jednym jedynym momencie (w chwili wystąpienia zbocza aktywnego), natomiast przerzutnik latch przepuszcza na wyjście dane nie w jednej chwili, ale przez cały czas podawania na wejście sterujące poziomu aktywnego. Mówimy, że podczas podawania na wejście sterujące poziomu aktywnego, latch jest przezroczysty. Przezroczysty, to znaczy stan wyjścia zmienia się zgodnie ze zmianami stanu na wejściu informacyjnym.

Natomiast gdy na wejściu sterującym pojawi się stan spoczynkowy, nieaktywny, to na wyjściu przerzutnika pozostaje stan, taki jaki tam był ostatnio. Mówimy, że przerzutnik nie jest już przezroczysty, tylko dane zostały zatrzaśnięte i pozostaną tam bez zmian aż do pojawienia się stanu aktywnego na wejściu sterującym.

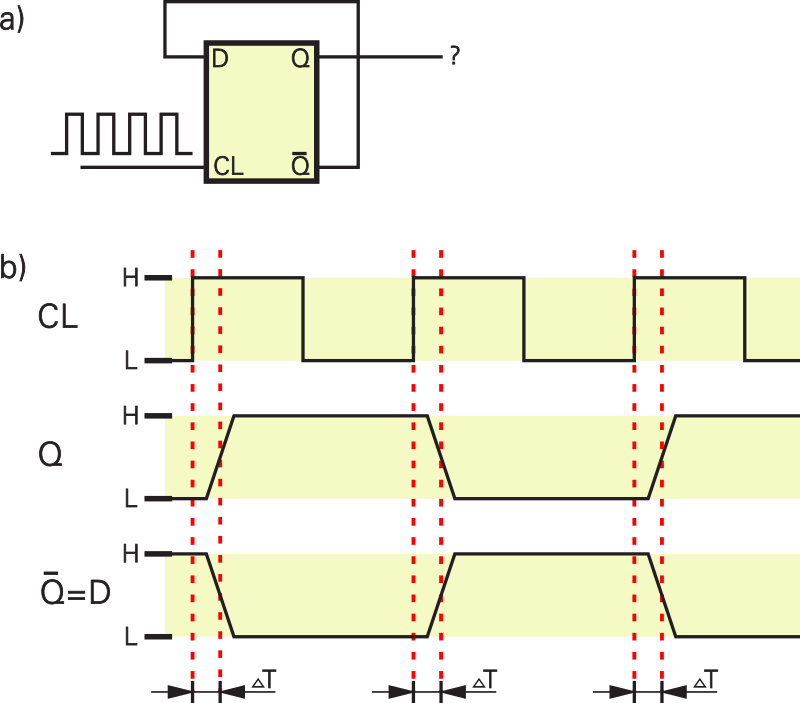

Działanie zatrzasku sterowanego poziomem możesz prześledzić na rysunku 1.

Przerzutnik typu zatrzask (latch) sterowany poziomem nie ma specjalnego oznaczenia graficznego. Czasem spotyka się oznaczenie identyczne jak klasycznego przerzutnika D sterowanego zboczem. Przecież nadal sygnał z wejścia informacyjnego jest przepisywany na wyjście pod wpływem sygnału zegarowego, stąd uzasadniona obecność oznaczeń D – data i CL – clock.

Wśród kostek rodziny CMOS 4000 nie ma pojedynczych przerzutników latch (sterowanych poziomem). Jest natomiast kostka 4042 zawierająca cztery takie przerzutniki ze wspólnym wejściem sterującym (dla wygody wyposażonym w bramkę EX−OR, co umożliwia użytkownikowi samodzielny dobór poziomu aktywnego). Układ 4042 nie znajduje jednak zbyt wielu zastosowań i nie zawracaj sobie nim głowy. Wśród układów TTL dawniej popularny był układ 7475, ale dziś także używany jest bardzo rzadko, może nawet wcale.

Obecnie częściej stosowane, zwłaszcza w technice mikroprocesorowej, są układy 74373 i 74573, zawierające zespół ośmiu latchów (czyt. laczów) ze wspólnym wejściem sterującym. Pomimo podobieństw, a niekiedy możliwości wymiennego stosowania, układy 74373 i 74573 sterowane poziomem, należy odróżniać od wcześniej wspomnianych kostek 74374 i 74574, zawierających osiem sprzężonych przerzutników D sterowanych zboczem.

W praktyce dość często spotykamy się też z przerzutnikami latch, ale wbudowanymi w bardziej złożone układy scalone. Na przykład dekodery do sterowania wyświetlaczy siedmiosegmentowych, takie jak 4511, czy znacznie bardziej popularny 4543, a także niektóre rejestry, wyposażone są w przerzutniki latch, które pełnią rolę swego rodzaju pamięci. Przykładowo dzięki zastosowaniu przerzutników, inaczej mówiąc pamięci, można uzyskać różne tryby wyświetlania informacji z licznika. Jeden tryb to praca z latchem, który jest przezroczysty. Stany licznika są na bieżąco pokazywane na wyświetlaczu. Taki tryb może być przydatny przy zliczaniu pojedynczych impulsów. W drugim trybie, podczas pracy licznika latch jest zatrzaśnięty, a wpisuje się do niego stany licznika dopiero po skończeniu cyklu pracy licznika. Potem gdy licznik rozpocznie nowy cykl pracy, dzięki zatrzaśnięciu poprzedniego wyniku zliczania, na wyświetlaczu pozostaje stabilne wskazanie. Nie ma migania wskaźnika podczas zliczania impulsów. Jeśli ostatnie zdania nie są dla ciebie zrozumiałe, nie martw się. Zrozumiesz wszystko, gdy zapoznasz się z licznikami i rejestrami.

Przerzutnik JK

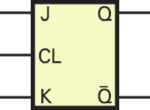

Symbol graficzny przerzutnika JK (inni piszą J−K) pokazany jest na rysunku 2.

Nie wiadomo dokładnie, skąd wzięły się literki JK. Niektórzy sądzą, że są to inicjały wynalazcy.

Także działanie przerzutnika JK niektórym początkującym wydaje się trudne do zrozumienia. Ale nie ma tu nic trudnego!

Przerzutnik JK na pewno jest wyzwalany zboczem. Na pewno posiada więc wejście zegarowe (oznaczane CL lub CLK) – tu przypomina przerzutnik D. W przeciwieństwie do przerzutnika D ma nie jedno, ale dwa wejścia informacyjne oznaczane J i K. Stan wyjścia (wyjść) zależy więc od stanów na wejściach informacyjnych J, K jakie występują tam w momencie wystąpienia zbocza aktywnego. To też jest beznadziejnie proste. A teraz uważaj!

Gdy w momencie wystąpienia na wejściu zegarowym zbocza aktywnego, na obu wejściach J i K jest stan niski, wtedy na wyjściu (wyjściach)… nic się nie zmienia – pozostają tam stany, jakie były tam wcześniej.

Gdy na wejściu J jest stan wysoki, a na K− niski, po przyjściu sygnału zegarowego wyjście główne Q ustawiane jest w stan wysoki.

Gdy na wejściu K jest stan wysoki, a na J – niski, po przyjściu sygnału zegarowego wyjście główne Q ustawiane jest w stan niski.

Gdy na obu wejściach J i K jest stan wysoki, wtedy po przyjściu aktywnego zbocza sygnału zegarowego stany wyjść Q i Q\… zmieniają się na przeciwne.

Może zastanawiasz się, po co komu taki dziwoląg? Wierz mi, że po pojawieniu się pierwszych przerzutników, właśnie z przerzutników JK budowano najróżniejsze liczniki i rejestry. Obecność wejścia zegarowego i wejść informacyjnych JK pozwala budować najróżniejsze układy i systemy synchroniczne. Co to znaczy synchroniczne?

Układ synchroniczny to taki układ logiczny, w którym stany wyjść poszczególnych przerzutników wchodzących w jego skład zmieniają się jednocześnie – praktycznie w momencie wystąpienia aktywnego zbocza sygnału zegarowego. Oczywiście sygnał zegarowy jest wspólny dla wszystkich przerzutników tego układu. Jeśli jeszcze nie bardzo rozumiesz, o co chodzi w tych układach synchronicznych nie załamuj się – zrozumiesz za jakiś czas. Na początku swojej przygody z cyfrówką nie musisz przecież wiedzieć wszystkiego.

Nie będę cię też wprowadzał w szczegóły budowy wewnętrznej przerzutników JK, jak nie wprowadzałem cię w szczegóły budowy przerzutników D. Ale o jednej sprawie muszę króciutko wspomnieć. Być może obiło ci się o uszy określenie przerzutnik JK typu master−slave (albo pan−sługa), ewentualnie JK flip−flop. Owo master−slave wskazuje, że przerzutnik zbudowany jest z dwóch części (a nawet z dwóch przerzutników), z których jedna pełni funkcje nadrzędną – master, a druga podrzędną – slave. Może też zasłyszałeś coś o przerzutnikach dwuzboczowych. W takich przerzutnikach jedno zbocze (o dziwo to nieaktywne) wpisywało stan wejść do pierwszego przerzutnika, a dopiero to drugie, aktywne przepisywało stan pierwszego przerzutnika do drugiego i na wyjścia. Przed wielu laty, na początku historii układów scalonych, w niektórych wypadkach konstruktor wręcz musiał zdawać sobie sprawę z pewnych niedostatków i nieoczekiwanych szczególnych właściwości poszczególnych układów scalonych. Trzeba było na przykład uwzględnić zjawisko tak zwanego łapania jedynek, które mogło w zadziwiający sposób zmienić działanie systemu zawierającego przerzutniki JK z niektórych układów scalonych. Na szczęście dziś nie trzeba się zastanawiać, co się dzieje w środku. Nie zaśmiecaj więc sobie głowy przerzutnikami dwuzboczowymi, czy łapaniem jedynek – wystarczy żebyś o przerzutniku JK wiedział to, co ci podałem wcześniej.

Obecnie pojedyncze przerzutniki JK nie znajdują już tak szerokiego zastosowania jak dawniej. Natomiast bardziej złożone układy zawierające te przerzutniki: liczniki (synchroniczne) oraz rejestry, dostępne są w postaci gotowych układów scalonych, w związku z czym też nie musisz martwić się o szczegóły budowy wewnętrznej.

W praktyce będziesz miał do czynienia przede wszystkim z „prawdziwym” przerzutnikiem JK z kostki 4027, ewentualnie w rzadkich przypadkach z co bardziej nowoczesnymi układami rodziny zgodnej z TTL (np. 109, 112).

Zauważ, że podobnie jak kostka 4013, układ 4027 zawiera dwa przerzutniki wyposażone dodatkowo w wejścia RS (które też mają priorytet przed wejściami J,K,CL). Pamiętaj, że jeśli nie wykorzystasz wejść RS, to powinieneś je zewrzeć do masy.

Przerzutnik T

Najprostszy przerzutnik typu T (toggle – przeskakujący) ma tylko jedno wejście zegarowe, sterowane (jednym aktywnym) zboczem i działa bardzo prosto. Każde kolejne aktywne zbocze zmienia stan wyjścia na przeciwny.

Podobnie, jak dla przerzutników D oraz JK, aktywnym zboczem może być albo zbocze rosnące, albo malejące. Do tej sprawy powrócimy przy omawianiu liczników.

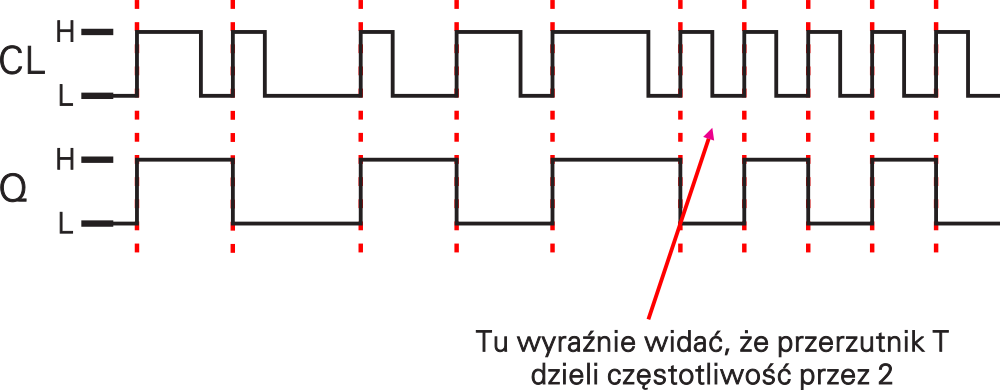

Rysunek 3 ilustruje działanie przerzutnika T sterowanego zboczem dodatnim (czyli rosnącym).

Na pewno zauważyłeś, że po podaniu na wejście zegarowe przerzutnika T przebiegu o jakiejś częstotliwości, na wyjściu uzyska się przebieg o częstotliwości dwa razy mniejszej.

W literaturze przerzutnik T często jest nazywany dwójką liczącą, bo proste liczniki (tak zwane asynchroniczne) buduje się właśnie z przerzutników typu T. Jeśli nie jesteś zupełnie „zielony” i trochę już miałeś do czynienia z cyfrówką, możesz uważać, że popularne liczniki 4020, 4040, 4060, 4518, 4520 zbudowane są właśnie z przerzutników T, a nie z przerzutników JK.

Przerzutniki T nie występują „w przyrodzie” pojedynczo. Nie znajdziesz kostki, która zawierałaby pojedyncze przerzutniki T. Nie musisz też szukać w literaturze symbolu graficznego przerzutnika T, zwykle przerzutnik T zaznacza się na schematach blokowych jednym ze sposobów pokazanych na rysunku 4.

W praktyce dość często będziesz potrzebował takich pojedynczych przerzutników, czy inaczej mówiąc, dwójek liczących. Nic straconego! Jak to zrobić?

Gratulacje! Tak jest! Jak słusznie zauważyłeś, przerzutnik T możesz zrobić z przerzutnika JK (np. 4027), podając na wejścia J i K stan wysoki. Ale nie tylko. Omówmy teraz sposób przeróbki przerzutnika D (4013) na przerzutnik T, a przy okazji wytłumaczę ci pewną bardzo ważną sprawę.

Najpierw popatrz na rysunek 5a (nie analizuj przebiegów z rysunku b) i powiedz mi, czy przy takim połączeniu rzeczywiście z przerzutnika D powstanie przerzutnik T?

Przeanalizuj działanie układu!

Coś ci się nie zgadza? Nie dziwię się, bo wielu początkujących ma z tym kłopoty.

Najprostsze rozumowanie jest takie: w momencie aktywnego zbocza na wejściu CL, do wyjścia Q przerzutnika wpisywany jest stan wejścia D, czyli wyjścia Q\. Przypuśćmy, że wcześniej na wyjściu Q był stan niski, a na Q\ – wysoki. W momencie zmiany na wyjściu Q pojawi się więc stan wysoki, a na Q\ – stan niski. Ale czy ten stan niski nie spowoduje natychmiastowej dalszej zmiany i czy w efekcie przerzutnik nie przekształci się w generator?

Nie! Wszystko będzie w porządku – rzeczywiście uzyskamy przerzutnik T, a wszystko to dzięki pewnym niewielkim opóźnieniom, tak charakterystycznym dla wszelkich realnych, a nie teoretycznych układów. Rzeczywiście, gdyby między wejściami a wyjściami przerzutnika nie było żadnych opóźnień, to nie potrafilibyśmy przewidzieć, co się będzie działo w układzie z rysunku 5a. Zajmijmy się więc tymi opóźnieniami. Każda realna bramka (składająca się z kilku tranzystorów) daje na wyjściu sygnał, który jest opóźniony względem stanów podawanych na wejście. Tak samo każdy przerzutnik, również złożony w sumie z tranzystorów, charakteryzuje się pewnym czasem opóźnienia. Jak wiesz, są to czasy rzędu nanosekund. Takich różnic i opóźnień nie będziesz w stanie wykryć i zbadać typowym słabym oscyloskopem. W warunkach amatorskich aby zając się tematem od strony praktycznej musisz posiadać oscyloskop o lepszych parametrach. A jak się okazuje, często już tak niewielkie opóźnienia są albo dobrodziejstwem, albo częściej przekleństwem, uniemożliwiającym pracę urządzenia. W praktyce nierzadko się zdarza, że amator bezskutecznie szuka błędu w układzie i nigdy go nie znajdzie, właśnie dlatego, że zapomina o tych nanosekundowych opóźnieniach. Postaraj się więc dobrze zrozumieć tę sprawę, bo tym razem jedynie analiza na papierze, a nie pomiar rzeczywistego układu kiepskim oscyloskopem może odsłonić przyczynę kłopotów.

Jeśli zrozumiesz zagadnienie, to tym samym zainstalujesz sobie w wyobraźni bardzo, bardzo szybki oscyloskop, i będziesz umiał zanalizować mniej i bardziej skomplikowane układy cyfrowe nie tylko pod względem statycznym, ale i dynamicznym. Do tej pory analizowaliśmy działanie bramek ze strony statycznej, ale w przypadku przeróbki przerzutnika D na przerzutnik T musimy dokonać analizy parametrów dynamicznych.

Przeanalizujmy więc przebiegi czasowe z rysunku 5b. Zakładamy, że zbocze na wejściu zegarowym jest bardzo strome, to znaczy zmiana stanu z niskiego na wysoki trwa bardzo krótko, powiedzmy poniżej 1 nanosekundy. Z definicji, przerzutnik D zmienia stan pod wpływem zbocza, a więc w czasie zmiany stanu na wejściu zegarowym.

Tymczasem opóźnienie wewnętrznych obwodów przerzutnika, oznaczone na rysunku 5b przez ΔT, wynosi przynajmniej kilkadziesiąt nanosekund (dla kostki CMOS4013, bo np. układu 74ACT74 – tylko kilka ns).

A więc jeszcze przez kilkadziesiąt nanosekund po wystąpieniu aktywnego zbocza, na wyjściach Q i Q\ będzie się utrzymywał „stary stan”. Tym samym „nowy” stan, wpisany z wejścia D pojawi się na wyjściach Q i Q\ po tym czasie opóźnienia ΔT. W momencie, gdy na wejściu D pojawi się opóźniony „nowy” stan, na wejściu zegarowym nie będzie już zmian, tylko będzie tam panował stan wysoki. Tym samym sygnał, że tak powiem, nie zapętli się, nie powstanie żaden generator, tylko na wyjściach pozostanie „nowy” stan aż do przyjścia następnego sygnału zegarowego.

Przy okazji jak na dłoni masz sprawę maksymalnej częstotliwości pracy przerzutnika T. Oczywiście maksymalna częstotliwość pracy będzie zależeć od czasu opóźnienia między wejściami a wyjściem. Czym dłuższe opóźnienie, tym mniejsza maksymalna częstotliwość pracy. Nieprzypadkowo narysowałem też mniej strome zbocza na wyjściach Q i Q\ – czas jaki upływa między przejściem napięcia na wyjściu od jednego „czystego” stanu logicznego do drugiego, wynosi kilka do kilkudziesięciu nanosekund.

Czasy opóźnienia (propagacji) w układach CMOS zależą od wartości napięcia zasilającego – czym większe napięcie, tym te czasy są krótsze. Przykładowo według katalogu, krajowe układy MCY74013 mają następujące typowe czasy opóźnienia (ΔT) między wejściem CL a wyjściami przy różnych napięciach zasilających: 5 V→150 ns; 10 V→100 ns; 15 V→45 ns. Tym samym maksymalna częstotliwość pracy przerzutnika (np. w roli przerzutnika T), czyli maksymalna częstotliwość na wejściu zegarowym jest różna dla różnych napięć zasilania. Ten sam katalog podaje, że częstotliwość ta wynosi: 5 V→7 MHz; 10 V→16 MHz; 15 V→24 MHz.

Nie myśl jednak, że wszystkie układy CMOS rodziny 4000 mogą pracować przy dużych częstotliwościach, ponad dziesięciu megaherców. Tak duże częstotliwości pracy są możliwe jedynie w przypadku stosunkowo prostych układów, takich jak bramki czy pojedyncze przerzutniki. Nietrudno się domyślić, że jeśli w układzie występuje więcej przerzutników i bramek, to ich czasy opóźnienia się sumują i znacznie ograniczają maksymalną częstotliwość pracy. W praktyce z wielu względów (nie tylko z powodu dużego czasu opóźnienia, ale też z uwagi na znaczny wzrost poboru prądu wraz z częstotliwością) układy CMOS4000 wykorzystuje się jedynie przy częstotliwościach co najwyżej 500 kHz…1 MHz. Przy większych częstotliwościach korzystniej jest zastosować kostki z rodzin: 74HC, 74HCT, 74AC, 74ACT, czy 74F.

A kolejny odcinek znajdziesz tutaj.

Piotr Górecki