Moja droga do okiełznania szybkich sygnałów

Cykl ten opowiada o mojej coraz większej świadomości dotyczącej zjawisk falowych, a szczególnie dopasowania falowego. Zjawiska te nabierają coraz bardziej znaczenia w moim projekcie komputera TTL, ze względu na to, że będzie on zbudowany z wykorzystaniem szybkich układów cyfrowych.

To jest druga cześć dużego artykułu, który ze względu na swoją obszerność został podzielony na trzy części. W poprzednim wykładzie przedstawiłem moje wyniki testów dotyczących statycznych właściwości buforów cyfrowych z różnych rodzin TTL. Testy te rzuciły światło na pewne ograniczenia i problemy kompatybilności połączeń różnych rodzin układów cyfrowych.

W tej części skupię się na szczegółowym wyjaśnieniu terminacji szeregowej, która będzie wieść prym w moim komputerze TTL. Przedstawię wady i zalety tego jednostronnego dopasowania. Mam wielką nadzieję, że dla wielu Czytelników terminacja ta zyska przy bliższym poznaniu.

W ostatniej części przedstawię wyniki testów właściwości dynamicznych szybkich buforów cyfrowych. Dzięki analizie tych testów wyciągnę istotne wnioski, które z pewnością zmaterializuję w fizycznym projekcie mojego komputera. Testy te zostaną przeprowadzone przy użyciu płytki, która całkowicie odbiega od prawidłowych zasad projektowania dla szybkich sygnałów. Dzięki temu będzie można się przekonać, jakie dodatkowe problemy stwarzają płytki PCB, które są nieprawidłowo zaprojektowane.

Terminacja szeregowa – nie ma czego się obawiać!

Ideę terminacji szeregowej prezentuje rysunek 1. Sposób ten jest powszechnie wykorzystywany w technice cyfrowej. Również terminacja szeregowa będzie wiodła prym w moim komputerze TTL, jako sposób na radzenie sobie z odbiciami sygnału – jednak w tym przypadku wykorzystam te odbicia na swoją korzyść, co jest z pewnością pozytywną cechą tej metody.

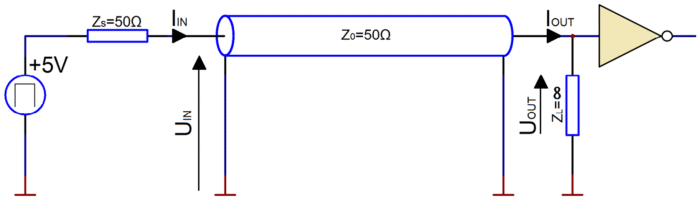

Na rysunku 1 widzimy źródło sygnału generujące impuls prostokątny. Jest to hipotetycznie idealne źródło, dlatego przyłączony jest do niego rezystor szeregowy ZS/bo rezystancji 50 Ω. Dzięki temu źródło jest dopasowane od strony wejścia linii transmisyjnej, której impedancja charakterystyczna Z0 również wynosi 50 Ω. Dopasowanie nie występuje na wyjściu linii transmisyjnej. Jest tam przyłączony inwerter CMOS, którego impedancja wejściowa jest ogromna, symbolicznie prezentuje to rezystor ZL. Zanim opowiem, co się dalej dzieje zerknijmy na rysunek 2.

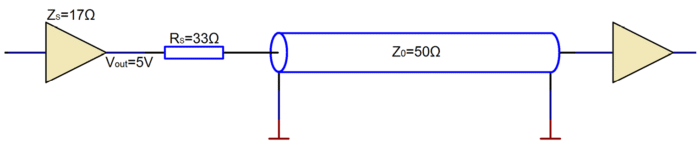

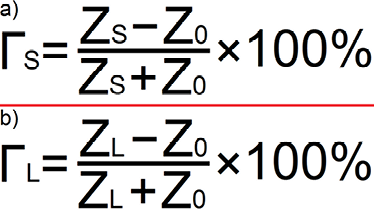

Rysunek ten przedstawia bardziej realną sytuację, gdzie impedancja ZS drivera, wynosząca 17 Ω, łączy się szeregowo z rezystancją RS o wartości 33 Ω. Dzięki temu mamy dopasowanie na wejściu linii transmisyjnej. Nie występuje tam żadne odbicie, co potwierdza wzór na rysunku 3a.

Gdy podstawimy do niego wartości ZS (w tym przypadku połączenie szeregowe impedancji wyjściowej drivera i rezystora szeregowego) oraz Z0, otrzymamy 0% odbicie na wejściu linii. Współczynnik odbicia ΓS wynosi 0.

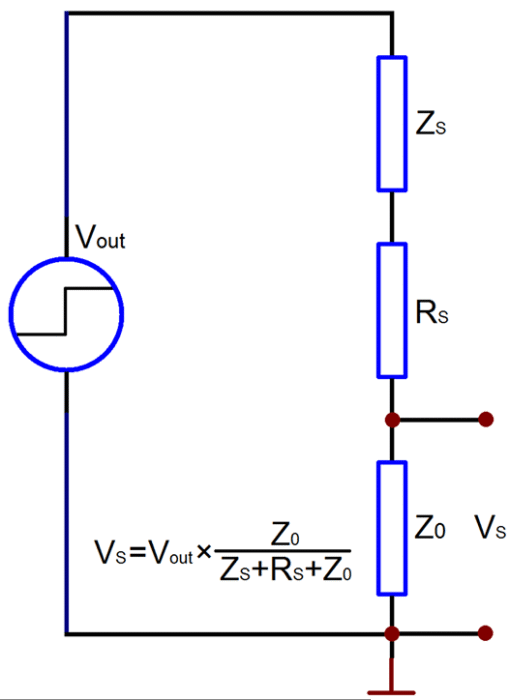

Oprócz dopasowania, które chcieliśmy osiągnąć i osiągnęliśmy, mamy jeszcze jedną konsekwencję takiego połączenia. Otóż na wejściu linii długiej tworzy się nam dzielnik napięcia, na który składają się: impedancja charakterystycznaZ0 linii długiej oraz szeregowe połączenie impedancji wyjściowej drivera ZS z rezystancją szeregową RS. Schematycznie tę sytuację przedstawia rysunek 4.

Jak łatwo obliczyć, gdy na wyjściu generatora VOUT pojawi się napięcie w wysokości 5 V, dzielnik ten spowoduje, że na wejściu linii transmisyjnej napięcie VS będzie miało wartość 2,5 V. I to jest dosyć intuicyjne, bo rysunek 4 przedstawia klasyczny dzielnik napięcia, utworzony z trzech rezystorów, które symbolizują wspomniane komponenty. Wykorzystujemy tu czysto elektrotechniczne obliczenia.

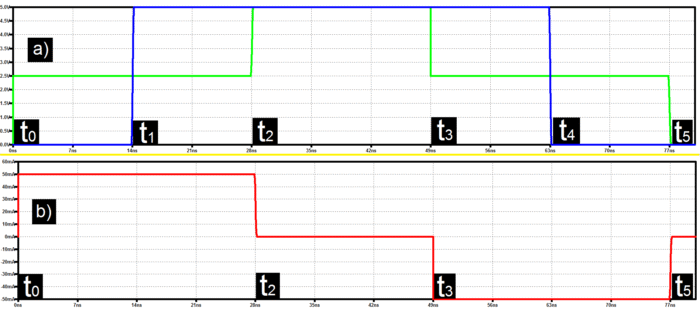

Jednak napięcie o takiej połowicznej wartości nie będzie się tam zbyt długo utrzymywać, co już nie jest do końca intuicyjne… Spójrzmy ogólnie na rysunek 5, który jest symulacją obwodu z rysunku 2. Rysunek 5 przedstawia przebiegi napięcia na wejściu i wyjściu linii transmisyjnej oraz przebieg prądu na jej wejściu. Czas propagacji linii długiej wynosi 14 ns, a czas trwania impulsu prostokątnego 49 ns.

(…)

——– ciach! ——–

To jest tylko fragment artykułu, którego pełna wersja ukazała się w sierpniowym numerze czasopisma Zrozumieć Elektronikę (ZE 9/2025). Pełną wersję czasopisma znajdziesz pod tym linkiem. Natomiast niepełna, okrojona wersja, pozwalająca zapoznać się z zawartością numeru ZE 9/2025 znajduje się tutaj.

Rafał Wiśniewski

rafi8112@interia.pl

Uwaga! Wskazówki, jak nabyć pełne wersje dowolnych numerów ZE znajdują się na stronie:

https://piotr-gorecki.pl/n11.