Pierwsze kroki w cyfrówce – część 5

W poprzednim odcinku przedstawiłem ci ogólne wiadomości o układach cyfrowych, zajęliśmy się też układami standardowymi z serii TTL – wykonanymi przy użyciu tranzystorów bipolarnych. W tym odcinku przedstawie ci garść interesujących informacji o układach scalonych z serii CMOS – wykonanych przy użyciu tranzystorów MOSFET.

CMOS

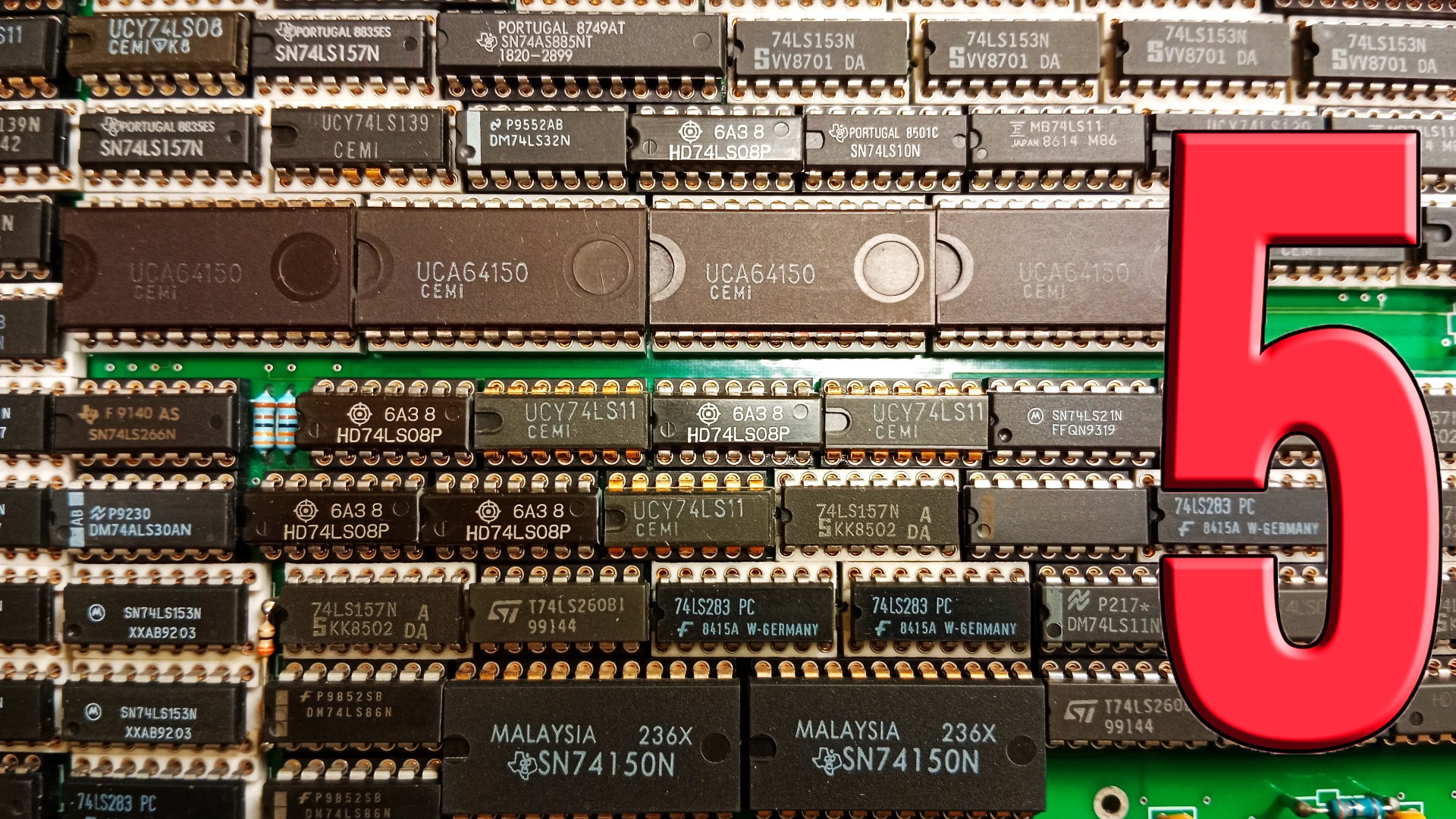

Układy TTL rodzin: 74, 74L, 74H i 74S wykonane były ze „zwykłych”, czyli bipolarnych tranzystorów.

Równocześnie podjęto próby wykorzystania do budowy układów cyfrowych tranzystorów unipolarnych z izolowaną bramką, czyli tranzystorów MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Pojawiły się układy logiczne zbudowane z wykorzystaniem tranzystorów polowych MOSFET z kanałem N oraz układy z MOSFET-ami z kanałem P. Nie przyjęły się jednak na rynku.

Z upływem czasu opanowano technologię wykonywania w jednej kostce zarówno tranzystorów komplementarnych: p−MOS i n−MOS, czyli technologię CMOS (Complementary MOS).

Szybko okazało się, że układy scalone zbudowane w technologii CMOS mają niezaprzeczalne zalety. Najważniejszą jest fakt, że w stanie spoczynku praktycznie nie pobierają prądu ze źródła zasilania, oraz że wejścia też nie wymagają przepływu prądu.

Nieco uproszczony schemat wewnętrzny bramki NAND w wersji CMOS pokazany jest na rysunku 1.

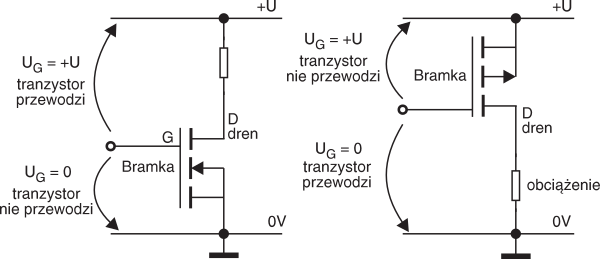

Dla niewtajemniczonych przygotowałem rysunek 2 ilustrujący działanie tranzystorów MOSFET z kanałem N i kanałem P. Tranzystory te przypominają nieco komplementarne tranzystory NPN i PNP, ale sterowane są napięciowo, to znaczy w obwodzie bramki nie płynie prąd.

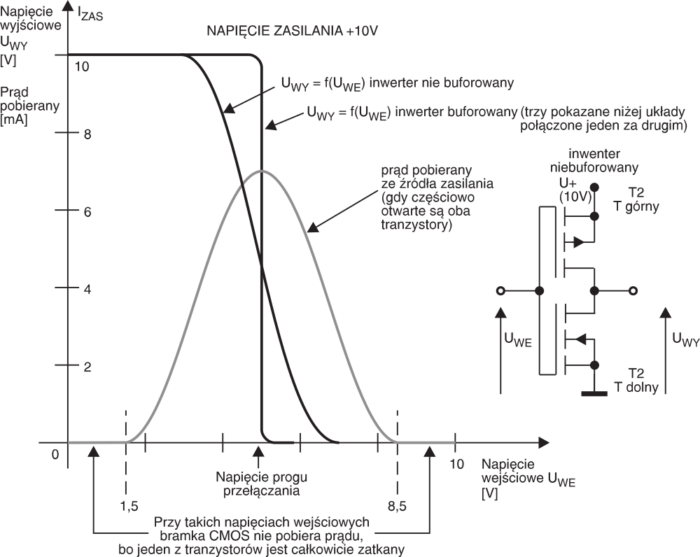

Jasne jest, że w bramce wykonanej technologią CMOS, gdy napięcie wejściowe jest równe potencjałowi masy albo potencjałowi zasilania, jedne tranzystory są otwarte, inne zamknięte. Prąd ze źródła zasilania nie płynie. Natomiast przy zmianie stanu na wejściu(ach), tranzystory włączają i wyłączają się płynnie, a więc przez czas gdy napięcie ma pośrednią wartość, przewodzą zarówno tranzystory z kanałem N, jak i P. Na rysunku 3 zobaczysz nieco uproszczoną charakterystykę przejściową bramki inwertera CMOS, przy czym dodatkowo zaznaczyłem tu pobór prądu zasilania w zależności od napięcia wejściowego.

W praktyce zmiany stanów logicznych są bardzo szybkie, więc układy CMOS pobierają ze źródła zasilania krótkie, szpilkowe impulsy prądu w momencie przełączania. W sumie pobór prądu przez układy CMOS zależy od częstotliwości przełączania, a także od wspomnianej wcześniej szkodliwej pojemności obciążenia − spójrz na rysunek 11 w poprzedniej części.

Widzimy tu ogromne zalety układów CMOS:

1.w spoczynku prąd zasilający jest równy zeru − rośnie on liniowo ze wzrostem częstotliwości przełączania.

2.wejścia układów CMOS sterowane są napięciowo i nie płynie tam żaden prąd (z wyjątkiem prądu potrzebnego do przeładowania pojemności wejściowej bramek, równej 5…10 pF).

Niestety, pierwsze układy CMOS miały liczne wady. Pomimo tych wad, zalety przeważyły i układy CMOS bardzo szybko stały się popularne.

Wady pierwszych układów CMOS

Najważniejszą wadą pierwszych „cemosów” była wielka podatność na uszkodzenia przez ładunki statyczne. Związane to było z bardzo cienką warstwą izolacyjną między bramką, a kanałem tranzystorów MOSFET. Warstewka ta łatwo ulegała nieodwracalnemu przebiciu pod wpływem wysokiego napięcia. Takie wysokie napięcia występują powszechnie wokół nas. Doświadczamy tego, niekiedy nawet boleśnie, gdy nasze ubranie naelektryzuje się i podczas jego zdejmowania, czy też przy dotknięciu klamki wręcz przeskakują iskry. Co prawda zgromadzony ładunek elektryczny jest niewielki, ale napięcie sięga kilku tysięcy woltów. Takie ładunki, zwane statycznymi były zmorą użytkowników pierwszych „cemosów”. Wystarczyło dotknąć palcem wyprowadzeń kostki, i można ją było wyrzucić do kosza. W tamtych czasach przy montażu i uruchomianiu układów zawierających kostki CMOS stosowano szereg zabezpieczeń, takich jak uziemianie całego stanowiska i metalowego blatu stołu, a także uziemienie człowieka za pomocą przewodzącej bransolety na rękę.

Z czasem wprowadzono skuteczne zabezpieczenia wejść. Ale i dziś w każdym katalogu można znaleźć zalecenia zachowania daleko idących środków ostrożności, a kostki CMOS pakowane są bądź w przewodzącą gąbkę, bądź w antystatyczne, czyli też trochę przewodzące plastikowe szyny, zwane potocznie laskami.

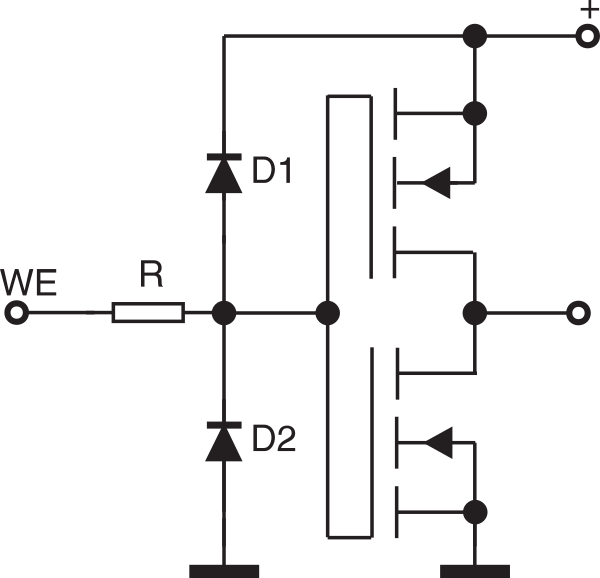

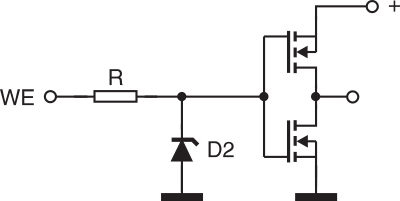

Klasyczny obwód zabezpieczenia wejścia kostki CMOS pokazany jest na rysunku 4.

Rezystor ogranicza prąd, a napięcie na bramce nie może zanadto wzrosnąć, bo prąd popłynie przez jedną z diod do którejś z szyn zasilających. Zabezpieczenie jest 100−procentowo skuteczne, gdy obie szyny zasilające są ze sobą zwarte, albo przynajmniej połączone rezystorem o niewielkiej wartości, bądź kondensatorem. W praktyce przy montażu układów CMOS na płytce drukowanej, zaleca się wlutowanie na początek wszystkich kondensatorów odsprzęgających zasilanie, a potem przy lutowaniu kostki, lutowanie w pierwszej kolejności nóżek zasilania. Dziś prawie nikt nie przestrzega zalecanych środków ostrożności i lutowane układy jakoś nie ulegają uszkodzeniu. Ja osobiście nie jestem przewrażliwiony na tym punkcie, ale jeśli ktoś chce przestrzegać zalecanych środków ostrożności − na pewno na tym nie straci. Nie zaszkodzi na przykład uziemienie stanowiska pracy, grota lutownicy czy posługiwanie się zalecanym przez MacGyvera arkuszem czarnej gąbki przewodzącej. Ale nie należy tu przesadzać, no chyba, że montuje się wyjątkowo kosztowne układy − wtedy ostrożności i uziemiania nigdy za dużo.

Drugą poważną wadą pierwszych „cemosów” było występowanie zjawiska zatrzaskiwania − w literaturze określa się to mianem latch−up. Rzecz w tym, że w układzie scalonym oprócz elementów pożądanych, zaznaczonych na schemacie, zawsze występują dodatkowe struktury i złącza. Związane to jest z procesem wytwarzania wielu elementów w jednym płatku krzemu. W pewnych warunkach te dodatkowe struktury zachowują się jak tyrystor i raz wyzwolone zaczynają przewodzić prąd. Aby przywrócić normalną pracę, należy na chwilę wyłączyć zasilanie.

Wyzwolenie wspomnianego pasożytniczego „tyrystora” następuje podczas przepływu nadmiernego prądu w obwodach wejść lub wyjść. Właśnie między innymi dlatego w katalogach układów CMOS podaje się maksymalny prąd wejściowy (rzędu 10…20 mA).

O jaki prąd tu chodzi, przecież wejścia „cemosów” mają wcale nie pobierać prądu? Na rysunku 4 pokazałem ci obwód zabezpieczenia wejścia. W rzeczywistości układ zastępczy jest bardziej skomplikowany i oprócz pokazanych diod, w obwodach wejść występują jeszcze inne złącza. Jeśli mówimy o prądzie wejścia, chodzi o prąd, płynący przez te dodatkowe złącza od końcówki wejściowej do jednej z szyn zasilania. Prąd taki popłynie jedynie wtedy, gdy napięcie na końcówce wejściowej będzie większe niż dodatnie napięcie zasilające, albo mniejsze niż ujemne napięcie zasilające. Pokazuje to rysunek 4. Przeanalizuj dokładnie ten schemat. Czasami się zdarza, że napięcie na wejściu kostki CMOS jest większe, niż napięcie zasilające tę kostkę. Wtedy prąd płynie przez diodę zabezpieczającą do… źródła zasilania. Czy jest to groźne? W sumie nie, o ile tylko nie zostanie przekroczony dopuszczalny prąd wejściowy (w praktyce przyjmuje się dopuszczalną wartość równą 10 mA). Przy takich prądach wejściowych zjawisko latch−up w obecnie produkowanych układach scalonych na pewno nie wystąpi i naprawdę nie trzeba się go obawiać.

Ale istnienie obwodu zabezpieczającego (rysunek 4) miewa jeszcze inne konsekwencje praktyczne.

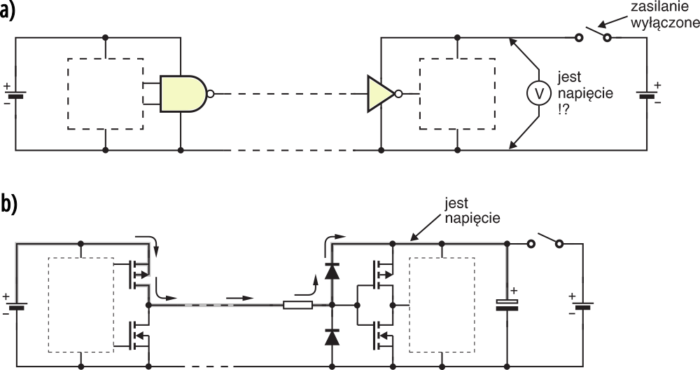

Mianowicie początkującym „cyfrowcom” czasem zdarza się sytuacja, której nie potrafią wyjaśnić. Wygląda na to, że w układzie w cudowny sposób pojawia się napięcie zasilające. Sytuacja pokazana jest na rysunku 5.

Rysunek 5a pokazuje ten zadziwiający efekt. Rysunek 5b wyjaśnia sprawę: prąd płynie przez jedno z wejść, przez diodę zabezpieczającą do dodatniej szyny zasilania i ładuje kondensatory filtrujące napięcie. Wszystko to jest możliwe, bowiem pobór prądu przez układy CMOS jest niewielki i do zasilania układu wystarczy niewielki prąd płynący przez jedno z wejść.

Czy taki sposób zasilania wykorzystuje się w praktyce? Raczej nie, ale o zjawisku trzeba wiedzieć. Może ono bowiem być bardzo niepożądane. Przykładowo, ktoś chciałby zmniejszyć pobór prądu jakiegoś rozbudowanego systemu, zasilanego z baterii lub akumulatorów. Postanawia więc odłączyć zasilane części układu. I co? Pomimo przerwania obwodu zasilania, wskutek omawianego zjawiska płynie znaczny prąd przez wyjścia układów współpracujących z „wyłączoną” częścią urządzenia.

Ponadto często współpracują ze sobą dwa systemy cyfrowe, zasilane napięciami o różnej wartości. Łatwo się domyślić (porównaj rysunek 5b), że z wyjść układu zasilanego wyższym napięciem będą płynąć prądy przez wejścia układów zasilanych niższym napięciem.

Co zrobić? Przewidując nietypowe zastosowania, producenci układów CMOS zaprojektowali dwie kostki, które mają inny obwód zabezpieczenia wejścia. Obwód ten pokazany jest na rysunku 6. Tym razem nie ma diody dołączonej do dodatniej szyny zasilania i nie wystąpi przepływ prądu do tej szyny. Szczegóły podam ci przy omawianiu bramek rodziny CMOS4000.

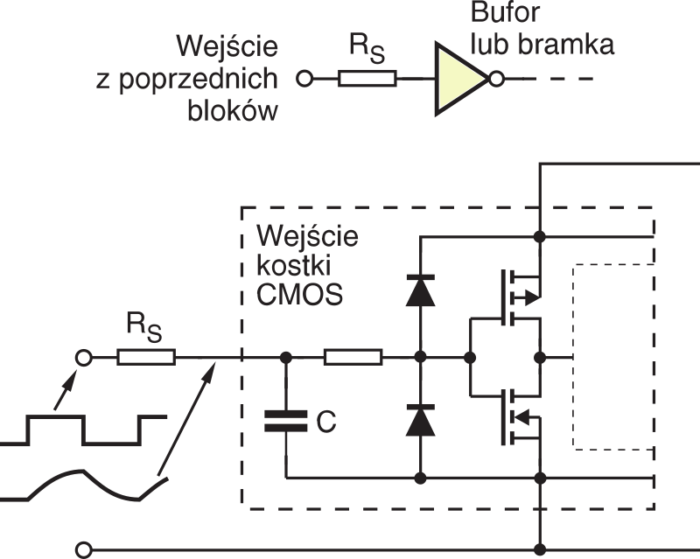

Ale najprostszym, często stosowanym sposobem uniknięcia niespodzianek jest włączenie na wejściu układu CMOS dodatkowego rezystora szeregowego Rs o rezystancji nie większej niż 10 kΩ − patrz rysunek 7.

Rezystor ten nie powinien mieć jednak wartości dużo większej niż 10 kΩ , bowiem należy pamiętać, że wejście każdego układu CMOS ma pewną pojemność, którą trzeba przeładować przy zmianie stanu logicznego. Pojemność ta jest rzędu 5…10 pF. Powstały obwód RsC opóźni więc sygnał, a przy bardzo dużej wartości Rs może nawet doprowadzić do szkodliwych drgań, o których wspomniałem wcześniej.

Z dotychczas podanych informacji wynika jasno, że wejścia wszystkich kostek CMOS mają zupełnie inne właściwości, niż wejścia układów bipolarnych TTL. Tłumaczyłem ci, że pozostawienie wejść TTL niepodłączonych, jest równoznaczne z podaniem stanu wysokiego. Wynika to z przyjętego rozwiązania układowego.

A jak to jest z wejściami kostek CMOS? Czy potrafisz samodzielnie odpowiedzieć na to pytanie?

Otóż wejść układów logicznych CMOS nie wolno pozostawiać niepodłączonych. W układach bipolarnych TTL w zasadzie można pozostawić niepodłączone wejścia, ale nie zaleca się tego, ze względu na ewentualne indukowane z zewnątrz zakłócenia. Natomiast nie sposób przewidzieć, jaki stan pojawi się na niepodłączonym wejściu kostki CMOS. Praktycznie nie płyną tam żadne prądy (prąd wsteczny diod zabezpieczających można pominąć). Oporność wejściowa jest bardzo duża i napięcie na pojemności wejściowej może się zmieniać pod wpływem zakłóceń. Często niepodłączona nóżka wejścia działa jak antena, zakłócenia powodują zmiany napięcia wejściowego i na wyjściu pojawia się przypadkowy przebieg zmienny, nierzadko o częstotliwości sieci 50 Hz. Takie niekontrolowane zmiany napięcia wejściowego i drgania zwiększają pobór prądu zasilania (porównaj rysunek 3).

Dlatego zapamiętaj raz na zawsze: nie wolno pozostawiać niewykorzystanych wejść typowych układów logicznych CMOS „wiszących w powietrzu”. Zawsze należy je łączyć albo do masy, albo do plusa zasilania − bezpośrednio lub przez rezystor 0…100 kΩ .

Tę zasadę mocno wbij sobie do głowy.

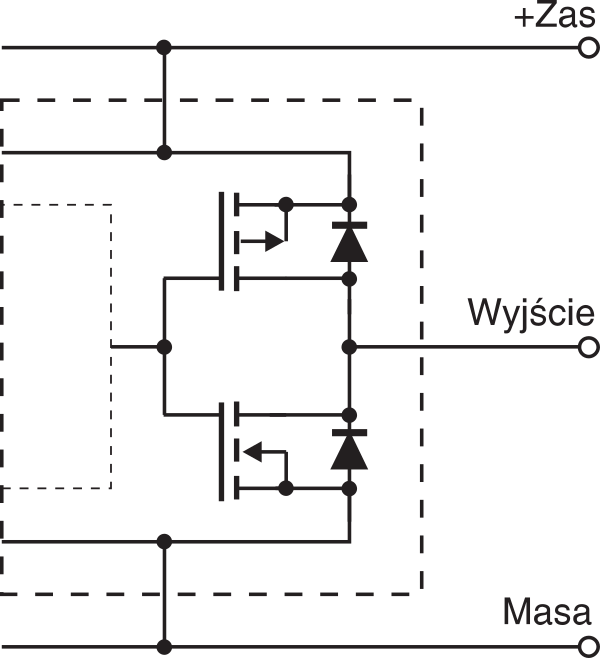

Teraz parę słów o wyjściach CMOS. W rzeczywistości w obwodach wyjściowych, oprócz tranzystorów, występują dodatkowe złącza − diody, pokazane na rysunku 8.

To pokazuje, że nawet przy próbie podania z zewnątrz na wyjście napięcia większego niż dodatnie napięcie zasilania (lub niższego niż potencjał masy), napięcie na tym wyjściu nie będzie większe od napięcia zasilającego o spadek napięcia na diodzie, czyli o około 0,7 V (niższe o 0,7 V od potencjału masy).

Krótko mówiąc, na wyjścia nie wolno podawać napięć (nawet krótkotrwałych przepięć) wykraczających poza napięcie zasilania − w skrajnym przypadku może to doprowadzić do wystąpienia wcześniej omówionego zjawiska zatrzaskiwania (latch−up).

Nastraszyłem cię tutaj możliwością uszkodzenia, zjawiskiem zatrzaskiwania i dziwnymi drogami prądu w kostkach CMOS. Przykro mi − jeśli chcesz być dobrym elektronikiem musisz dobrze rozumieć te sprawy, by nie popełnić błędów.

Rodziny układów CMOS

Jak ci wspomniałem, rozkład wyprowadzeń bipolarnej rodziny TTL74 szybko stał się niekwestionowanym standardem. Nie zdziwi cię więc informacja, że po opanowaniu technologii CMOS pojawiła się rodzina 74C obejmująca odpowiedniki kostek 74 wykonane w technologii CMOS − można je było poznać po literce C w oznaczeniu (74C00, 74C90). Wydawało się, że standardowi TTL wywodzącego się od rodziny 74 nic nie zagrozi.

Tymczasem przed ponad pięćdziesięciu laty firma RCA wprowadziła na rynek zupełnie inną rodzinę zwaną CMOS 4000. W kostkach tej rodziny układ wyprowadzeń był inny, niż w kostkach serii 74. Zaproponowano po prostu nowy standard. Ktoś mógłby pomyśleć, że nowy standard nie przyjmie się na rynku i na placu boju pozostaną tylko dobrze znane kostki (bipolarne i CMOS) w standardzie TTL. Stało się jednak inaczej.

Obecnie mamy więc następującą sytuację: na rynku występują generalnie dwie wielkie grupy. Jedna to kostki wywodzące się ze standardowej rodziny 74 (mające ogólnie rzecz biorąc, jednakowy układ wyprowadzeń). Początkowo wszystkie kostki wywodzące się od serii 74 były zasilane napięciem 5 V ±0,5 V i wykonane były w technologii bipolarnej. Obecnie spotyka się spokrewnione rodziny wykonane w technologii CMOS, mogące pracować w zakresie: od 2…6 V, a nawet przy napięciu zasilającym 1 V.

Druga duża grupa to kostki CMOS 4000. Kostki grupy CMOS4000 tworzą jedną rodzinę − nie ma tu różnych rodzin, na przykład: LS, H, C, itp.

Wszystkie kostki CMOS rodziny 4000 mogą być zasilane dowolnym napięciem z zakresu: 3…18 V

ECL

Przed laty produkowano też kilka innych rodzin układów logicznych, między innymi w technologii MOS. Ze względu na liczne wady nie zdobyły one popularności i nawet nie warto o nich wspominać.

Wyjątkiem jest oparta na tranzystorach bipolarnych rodzina ECL (Emiter Coupled Logic), która przez minione pięćdziesiąt lat rozwinęła się i do dziś jest obecna na rynku. Kostki ECL są najszybsze z powszechnie dostępnych. Ich czasy opóźnienia są rzędu nawet poniżej 1 nanosekundy, a więc układy te mogą pracować przy częstotliwościach powyżej 1 GHz. Kostki te praktycznie nie są używane przez amatorów.

Dalszy rozwój standardu 74

Rozwój grupy TTL, wywodzącej się od rodziny 74, poszedł w dwóch kierunkach. Jeden kierunek to poprawa szybkości i zmniejszanie mocy pobieranej przez układy zawierające „zwykłe”, czyli bipolarne tranzystory. Tu niepodzielnie zakrólowały tranzystory ze złączem Schottky’ego. (Szczegóły nie są istotne − tranzystory takie są po prostu szybsze od zwykłych npn i pnp.) Pojawiła się ro− dzina 74LS (Low−power Schottky). Przy szybkości takiej jak standardowe kostki 74, układy 74LS pobierają dziesięciokrotnie mniej mocy i mają dziesięciokrotnie mniejsze prądy wejściowe w stanie niskim. Kostki tej rodziny są bardzo popularne do dziś.

Pojawiła się rodzina 74F, która jest nieco szybsza od poznanej wcześniej rodziny 74S, ale pobiera dużo mniej prądu. Obecnie kostki te używane są w urządzeniach pracujących przy częstotliwości ponad 100 MHz.

Drugi kierunek rozwoju, to wykorzystanie zalet technologii CMOS. Choć rodzina 74C nie zagościła dłużej na rynku, szybko powstały rodziny: HC i HCT. Określenie HC(T) pochodzi od High−speed CMOS (TTL). Tu doszliśmy do ważnego momentu rozważań.

Czy domyślisz się sam, czym różnią się kostki HC i HCT?

Jest to ważna sprawa praktyczna, dlatego musimy sięgnąć do korzeni.

Nieprzypadkowo tłumaczyłem ci wcześniej, że wszystko zaczęło się od tak zwanej serii standardowej o oznaczeniu 74. Przyjęte wówczas rozwiązanie układowe narzuciło na wiele lat pewien standard. Nie chodzi tu o rozkład wyprowadzeń, tylko o parametry wejścia (i niektóre parametry wyjścia). Zarówno w układach serii standardowej, jak i w bipolarnych rodzinach pochodnych (74L, 74H, 74S, 74LS, 74F, 74AS), próg przełączania wejścia był na poziomie około 1,5 V, a dozwolone poziomy logiczne na wejściu były takie same: L=0…0,8 V, H=2,0…5,5 V. Analogicznie wydajność prądowa wyjść w stanie wysokim była kilkakrotnie mniejsza, niż w stanie niskim. Choć w późniejszych rodzinach można już było zastosować (i stosowano) zupełnie inne rozwiązania układowe, nadal trzymano się standardu, w którym w stanie niskim z wejść wypływa prąd, a pozostawienie wejść „w powietrzu” jest traktowane jako stan wysoki. Trzymanie się tych zasad nie wynikało już z ograniczeń technologii, a jedynie z potrzeby zapewnienia pełnej wymienności nowych i starych serii. To są właśnie te zaszłości, które ciągną się przez dziesięciolecia.

Jeszcze raz ci powtarzam − próg przełączania, dozwolone poziomy logiczne, traktowanie niepodłączonych wejść i kierunek prądu wejściowego w stanie niskim we wszystkich rodzinach kostek 74 zbudowanych z tranzystorów bipolarnych są takie same.

I oto weszła zupełnie inna technologia − CMOS. Przy sterowaniu napięciowym, gdy podczas pracy nie płynęły prądy wejściowe, aż się prosiło odejść od utartych standardów. Dotyczyło to przede wszystkim progu przełączania, przyjętych poziomów logicznych i wynikających z tego małych marginesów zakłóceń. Jeśli dwa tranzystory wejściowe (patrz rysunek 1) mają jednakowe parametry, wtedy próg przełączania bramki będzie wypadał w połowie napięcia zasilającego. Oczywiście zwiększy to marginesy zakłóceń i poprawi odporność na zakłócenia. Wydawało się, że przeniesienie progu przełączania z 1,5 V na połowę napięcia zasilającego (2,5 V) jest nieuniknione i oczywiste.

Ale konstruktorzy przyzwyczaili się przez lata do pierwotnego standardu (bipolarnego). Szczerze mówiąc, chyba głównie ze względu na to przyzwyczajenie, producenci układów cyfrowych wprowadzili dwie niemal identyczne rodziny CMOS: 74HC i 74HCT. Rodzina 74HC ma próg przełączania na poziomie 50% napięcia zasilającego, i (zapamiętaj to!) może być zasilana napięciem od 2…6 V.

Natomiast rodzina 74HCT jest reklamowana jako ścisły odpowiednik układów bipolarnych standardu TTL. W związku z tym zakres napięć zasilania ograniczono do 4,5…5,5 V, a próg przełączania wynosi, tak tak jak we wszystkich kostkach bipolarnych TTL − około 1,5 V. Osiągnięto to różnicując budowę wejściowych tranzystorów z kanałem P i N.

Ale na tym podobieństwa się kończą. Na wejściu nie wbudowano rezystora podciągającego, więc wejście sterowane jest napięciowo, i nie płyną tam żadne prądy. Jak ci tłumaczyłem, wejście pozostawione „w powietrzu” przyjmuje jakiś przypadkowy stan, zależny od prądów upływu wbudowanych diod zabezpieczających oraz od ładunku zgromadzonego na pojemności wejściowej bramki.

Jeszcze raz ci przypomnę, że w przeciwieństwie do bipolarnych układów TTL, we wszystkich kostkach CMOS (także 74HC i 74HCT) nie wolno pozostawiać niepodłączonych wejść − trzeba je połączyć z masą albo plusem zasilania.

Układy rodziny 74HCT (tak samo jak 74HC) mają symetryczne charakterystyki wyjściowe. To znaczy, że wydajności prądowe wyjść są takie same w stanie wysokim i niskim (w praktyce wydajność ta wynosi kilkadziesiąt mA).

Może zapytasz, po co tak duży prąd wyjściowy, jeśli następne wejścia wcale nie pobierają prądu? Kostki 74HC i 74HCT są szybkie, mogą pracować przy częstotliwościach do 40…60 MHz i duża wydajność prądowa pomaga szybko przeładować pasożytnicze pojemności pokazane na rysunku 7.

Opracowano także jeszcze szybsze rodziny CMOS, stanowiące konkurencję dla bipolarnej rodziny 74F. Kostki rodzin: 74AC, 74ACT (Advanced CMOS), 74ABT (Advanced BiCMOS − technologia mieszana, wykorzystująca w jednej kostce tranzystory bipolarne i MOSFET) mogą pracować przy częstotliwościach znacznie powyżej 100 MHz. Podobnie, jak w przypadku 74HC, rodzina 74AC ma zakres napięć zasilania 2…6 V i próg przełączania na poziomie połowy napięcia zasilającego. Rodzina 74ACT, analogicznie jak 74HCT, reklamowana jest jako ścisły zamiennik bipolarnych kostek TTL.

To nie koniec rozwoju kostek 74. Większość szybkich mikroprocesorów i pamięci zasilana jest napięciem rzędu 3 V i niższym. Wypuszczono więc kilka nowych rodzin układów 74. Nie są to rodziny zbyt liczne, bowiem zawierają jedynie układy sprzęgajace i sterujące, potrzebne do systemów komputerowych. Niektóre z tych kostek mogą być zasilane napięciem rzędu 1…1,3 V. A oto niektóre nowe rodziny: 74LV, 74LVC, 74LVT, 74HLL, 74ALVC, 74LCX.

Jako ciekawostkę podam informację, że niektóre z wymienionych niskowoltowych kostek zasilanych napięciem 3…3,6 V mogą bezpośrednio współpracować z kostkami zasilanymi napięciem 5 V. Jest to możliwe dzięki specyficznej budowie wejść i wyjść takich układów.

A kolejną część znajdziesz tutaj.

Piotr Górecki