Pierwsze kroki w cyfrówce – część 4

W poprzednim odcinku przedstawiłem ci tło zagadnienia, a także zapoznałem z podstawowymi cegiełkami − bramkami. Jeśli chcesz zajmować się elektroniką, koniecznie powinieneś „mieć w małym palcu” wszystkie wiadomości na temat bramek, podane w poprzednich dwóch odcinkach. Zanim przejdziemy do przerzutników, liczników, rejestrów, dekoderów, itp, musimy omówić pewną ważną kwestię. Właśnie w tym artykule podam ci bardzo istotne wiadomości. Nie przesadzam − są to informacje absolutnie niezbędne do świadomego i sensownego wykorzystania układów scalonych, nie tylko bramek.

Jeszcze raz czarna skrzynka

W poprzednich odcinkach wykazałem ci dokładnie, że działanie układów cyfrowych (logicznych) opiera się na pewnych podstawowych zależnościach matematycznych, i że układy te można zrealizować różnymi sposobami, także przy pomocy urządzeń mechanicznych i hydraulicznych.

W naszej praktyce mamy najczęściej do czynienia z układami scalonymi realizującymi mniej i bardziej złożone funkcje logiczne i cyfrowe. Stanom logicznym odpowiadają poziomy napięcia: jest napięcie − stan wysoki (1), brak napięcia − stan niski (0).

Często traktujemy układ logiczny (cyfrowy) jako czarną skrzynkę z wejściami i wyjściami, do której wchodzą jakieś sygnały cyfrowe, a po przetworzeniu wychodzą. W zasadzie interesuje nas tylko funkcja logiczna spełniana przez układ, natomiast nie chcielibyśmy zajmować się szczegółami realizacyjnymi, czyli dociekać, co jest w środku.

Ideałem byłoby, gdyby taka czarna skrzynka zupełnie nie pobierała prądu oraz żeby wejścia także nie pobierały prądu. Układ powinien też natychmiast realizować swą funkcję − nie powinno być żadnego opóźnienia między podaniem sygnału na wejście, a pojawieniem się odpowiedzi na wyjściu. Niestety, nie można zbudować aż tak doskonałych układów − nie pobierających mocy i nieskończenie szybkich.

Jaskrawie negatywnym przykładem są tu bramki zbudowane z przekaźników. Nie masz wątpliwości, że pobierają one dużo prądu i są stosunkowo wolne.

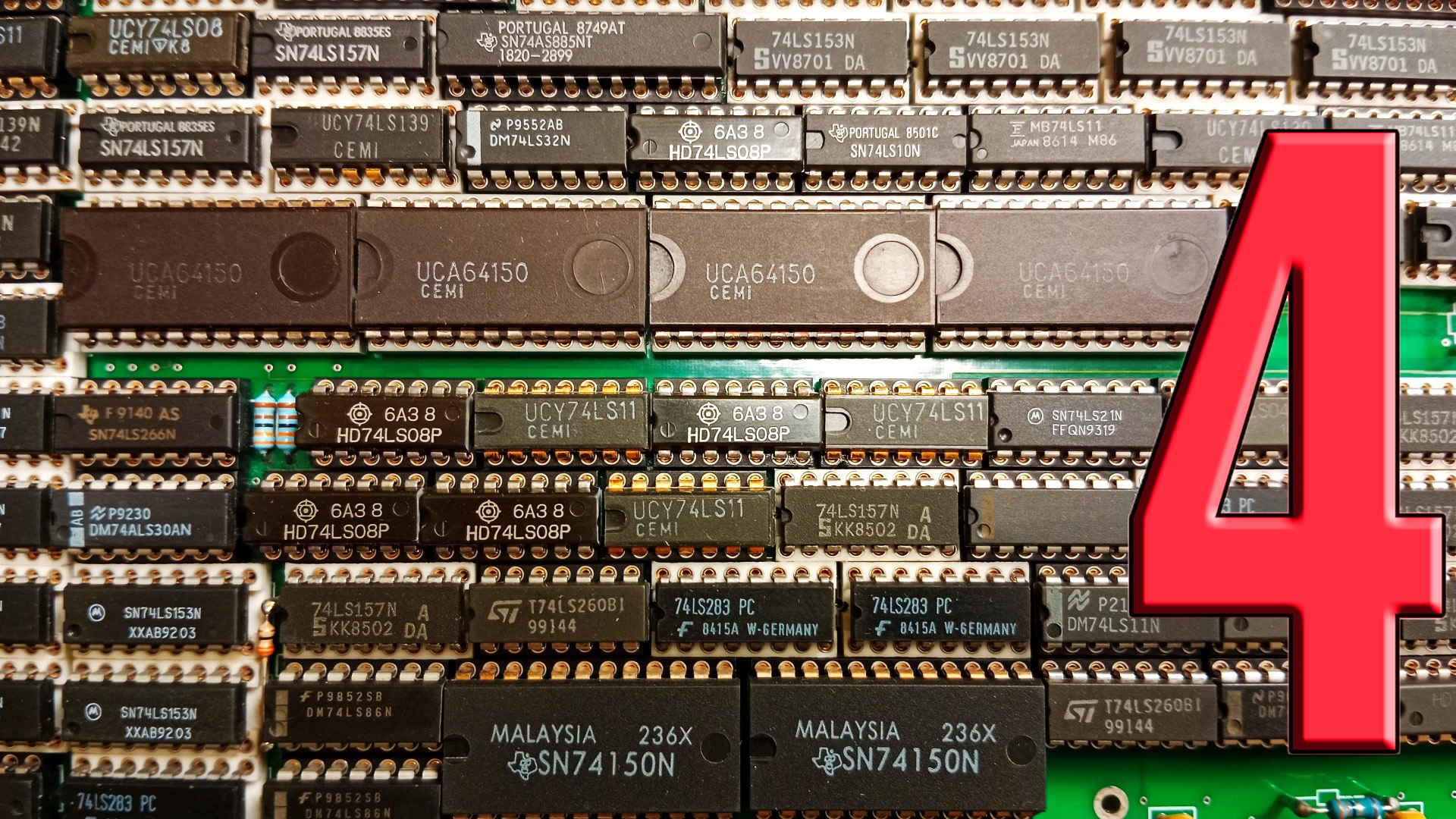

A jak to jest z bramkami na układach scalonych? Doszliśmy do sedna sprawy. Układy scalone też nie są doskonałe. Przykładowo, mamy do wyboru szereg różnych układów scalonych zawierających bramki NAND, że wymienię tylko kilka przykładów: 7400, 74LS00, 74HC00, 74HCT00, 74S00, 74F00, 74ACT00, 74LCX… Wszystkie wymienione kostki zawierają cztery dwuwejściowe bramki NAND, układ wyprowadzeń jest identyczny, czym więc się różnią?

Różnią się budową wewnętrzną. Dla nas praktyków, jest istotne, że bramki te różnią się szybkością, poborem prądu zasilającego, wielkością prądów wejść oraz wydajnością prądową wyjść. Parametry związane z poborem prądu i napięciami w stanie spoczynku nazywamy parametrami statycznymi. Parametry związane z szybkością − parametrami dynamicznymi.

Jeśli chcesz być prawdziwym elektronikiem, musisz dokładnie rozumieć te kwestie.

Dinozaury

Teraz zaczerpnij duży łyk świeżego powietrza, bo zanurzymy się w zatęchłą przeszłość. Niestety, muszę ci opowiedzieć o wymarłych już dinozaurach. Nie sprzeczaj się ze mną − w 2023 roku tak zwany „standardowy” układ TTL o oznaczeniu 7400 i jego pobratymcy są niewątpliwymi dinozaurami. Zaraz ci to wykażę.

A tymi archaicznymi stworami musimy się zająć, bowiem jak ci podałem w pierwszym odcinku, pojawienie się układów scalonych TTL było niekwestionowanym przełomem w dziedzinie układów logicznych. Choć od czasu pojawienia się pierwszych kostek tego typu minęło już prawie sześćdziesiąt lat, i pierwotne „standardowe” układy TTL stały się przeżytkiem, jednak pewne, że tak powiem, zaszłości, ciągną się od tamtych czasów aż po dzień dzisiejszy. I właśnie z uwagi na te zaszłości koniecznie musisz poznać układ… którego dziś już się nigdzie nie stosuje.

Pamiętaj, że układy TTL zasilano napięciem 5 V±0,5 V.

Rysunek 1 pokazuje schemat wewnętrzny tego dinozaura – bramki NAND 7400.

Diody D2 i D3 zabezpieczają wejście przed zakłóceniami. Podczas normalnej pracy są spolaryzowane zaporowo i można je pominąć przy analizie.

Na pewno niepokoi Cię obecność jakiegoś dziwaka − wieloemiterowego tranzystora T1 na wejściu. Takie rozwiązanie wejścia przyjęto między innymi ze względu na ówczesne możliwości technologiczne, czyli na łatwość wytwarzania.

Nas interesują napięcia i prądy wejściowe oraz wyjściowe.

Gdy oba wejścia bramki z rysunku 1 (7400) pozostawimy niepodłączone (potocznie mówimy: wejścia wiszą lub pływają w powietrzu), wtedy w obwodach emiterów tranzystora T1 nie może płynąć prąd. Tranzystor T1 pracuje wtedy w nietypowy sposób: prąd płynie od plusa zasilania, przez rezystor R1 i złącze baza−kolektor do bazy tranzystora T2. Trochę to dziwne, prawda? Tranzystor T2 przewodzi, co powoduje otwarcie tranzystora T3. Natomiast niskie napięcie na kolektorze T2 uniemożliwia przewodzenie tranzystora T4. Przewodzący tranzystor T3 daje na wyjściu napięcie praktyczne równe potencjałowi masy, czyli stan niski.

Czy już zauważyłeś, że w tej klasycznej bramce TTL niepodłączenie wejść (pozostawienie ich w powietrzu) jest równoznaczne z podaniem na te wejścia stanu wysokiego?

Przeanalizuj to jeszcze raz: dołączenie wejść do dodatniego napięcia zasilającego nic tu nie zmieni, bo w obwodach wejściowych nadal nie będzie płynął prąd przez złącza emitery−baza tranzystora T1 − złącza te będą spolaryzowane w kierunku zaporowym.

Dopiero zwarcie któregokolwiek wejścia (lub obu wejść) do masy, umożliwi przepływ prądu w obwodach emiterowych tranzystora T1. Prąd popłynie od plusa zasilania, przez rezystor R1, złącze baza−emiter i wejście(a) do masy. W takiej sytuacji nie będzie mógł płynąć prąd bazy tranzystora T2 i tranzystor T2 zostanie zatkany. Brak prądu płynącego przez tranzystor T2 zamknie też tranzystor T3. Natomiast prąd płynący przez rezystor R2 do bazy T4, otworzy tranzystor T4. Na wyjściu pojawi się napięcie zbliżone do dodatniego napięcia zasilającego, czyli stan wysoki.

Wracamy do obwodów wejściowych. Czy potrafisz samodzielnie odpowiedzieć na pytanie: jaki zakres napięcia na wejściach traktowany jest przez układ jako stan logiczny niski, a jaki zakres napięć odpowiada stanowi logicznemu wysokiemu?

Słusznie przypuszczasz, że napięcia od zera (potencjał masy) do około 1 V traktowane są jak stan logiczny niski − a wynika to z przyjętego rozwiązania układowego. W takim zakresie napięć wejściowych nie płynie prąd bazy tranzystora T2.

A jakie jest napięcie na wejściach, gdy są one „zawieszone w powietrzu” lub gdy między wejścia a masę włączona jest bardzo duża rezystancja?

Popatrz na rysunek 1. Na bazie przewodzącego tranzystora T3, napięcie wynosi około 0,7 V. Tranzystor T2 też przewodzi, więc na jego bazie napięcie wynosi około 1,4 V (w stosunku do masy). Przez złącze baza−emiter tranzystora T1 też płynie prąd, więc na bazie T1 napięcie będzie o następne 0,7 V wyższe, czyli wyniesie około 2,1 V. Teraz jest jasne, że woltomierz dołączony między niepodłączone wejścia, a masę wskaże około 1,4…1,5 V (to jest o 0,6…0,7 V mniej niż na bazie T1).

A więc napięcia rzędu 1,5 V i wyższe są traktowane przez układ jako stan logiczny wysoki.

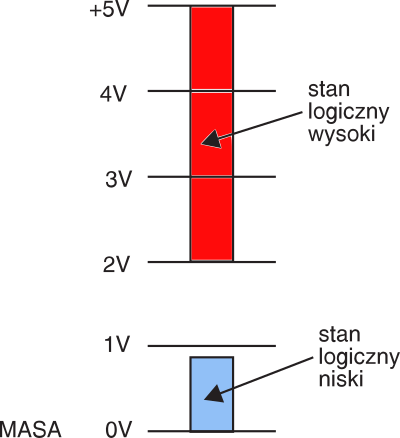

Na rysunku 2 zaznaczyłem z grubsza zakresy napięć odpowiadające stanowi logicznemu niskiemu i wysokiemu. Jeśli nie miałeś do tej pory do czynienia z układami cyfrowymi, to zapewne jesteś trochę zdziwiony taką niesymetrią. Nie masz chyba wątpliwości, że ta niesymetria wynika właśnie z przyjętego układu, czyli schematu wewnętrznego.

Ale to nie koniec niespodzianek; idźmy dalej.

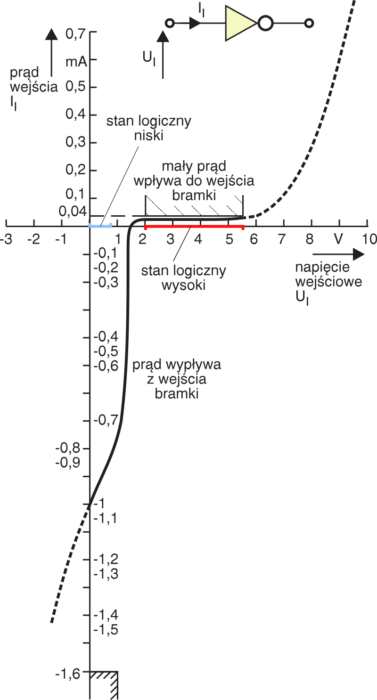

Wiesz już, że dla napięć większych niż 1,5 V przez wejścia praktycznie nie płynie prąd (w zasadzie wpływa tam bardzo mały prąd wstecznie spolaryzowanego złącza baza−emitery T1, prąd ten jest rzędu mikroamperów).

Natomiast dla napięć 0…1,4 V płynie prąd wejściowy. W którą stronę?

To bardzo ważne pytanie!

Prąd wejściowy wypływa z wejść i płynie do masy.

Wielkość tego wypływającego prądu wyznaczona jest wartością rezystancji R1; zależy też od napięcia wejściowego.

Rysunek 3 pokazuje charakterystykę wejściową bramki TTL. Tym razem napięcie wejściowe przedstawiono na osi poziomej. Jak widać dla napięć wejściowych większych niż 1,5 V prąd wejściowy jest dodatni, to znaczy wpływa do wejścia. Prąd ten jest bardzo mały, o ile tylko napięcie wejściowe nie jest większe od napięcia zasilającego układ (5…5,5 V).

Natomiast przy napięciach wejściowych mniejszych od 1,5 V prąd wejściowy jest ujemny, czyli wypływa z wejścia i jego wartość przy podłączeniu wejścia do masy wynosi około 1 mA.

Może powiesz, że 1 mA to bardzo mały prąd. Niby tak, ale jeśli w układzie scalonym chcielibyśmy upchnąć kilka tysięcy takich bramek, to już sam prąd wejść wynosiłby w sumie kilka amperów. A przecież prąd zużywany jest nie tylko w obwodzie wejściowym − przy stanie niskim na wyjściu prąd płynie także przez R2 i T2.

Tu znaleźliśmy istotną wadę standardowej bramki TTL − znaczny pobór prądu. Do tej sprawy za chwilę wrócimy.

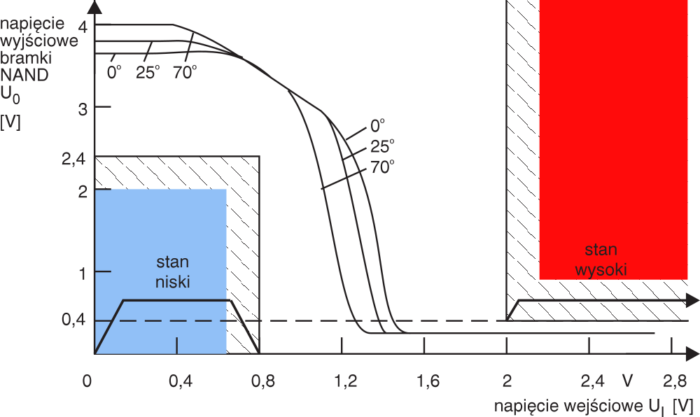

Na razie popatrz na rysunek 4. Przedstawia on charakterystykę przejściową bramki NAND z rodziny TTL. Z rysunku tego widać, że przy stanie niskim na wejściu, napięcie wyjściowe wcale nie jest równe napięciu zasilania, a ledwo sięga 4 V. To akurat nie jest żadną wadą, bowiem napięcie rzędu 3…4 V na pewno traktowane jest przez układy TTL jako stan logiczny wysoki.

Problem natomiast z zakresem przejściowym, przy napięciach wejściowych w okolicach 1,5 V. W tym zakresie napięć wejściowych bramka zachowuje się bowiem jak… wzmacniacz. Zauważ, że niewielkim zmianom napięcia wejściowego odpowiadają znacznie większe zmiany napięcia wyjściowego. Może cię to zdziwi, ale w pewnych warunkach bramka rzeczywiście jest po prostu wzmacniaczem (potem pokażę ci, jak tę „wadę” wykorzystuje się w praktyce).

No dobrze, ale przecież chyba ma to być dwustanowy układ logiczny, a nie jakiś wzmacniacz.

Istotnie, do tej pory milcząco zakładaliśmy, że wysoki stan logiczny to napięcie równe lub bliskie dodatniemu napięciu zasilającemu, a stan logiczny niski to napięcie bliskie zeru.

Teraz należałoby sprawę uściślić. I to są właśnie wspomniane przeze mnie wcześniej zaszłości, które ciągną się od pierwszych układów TTL aż do dziś.

Uważaj więc! Ze względu na rozwiązanie układowe przyjęte w pierwszych układach TTL ustalono, że na wejściach bramek mogą występować napięcia w zakresie: 0…0,8 V (co odpowiada niskiemu stanowi logicznemu) oraz w zakresie: 2…5,5 V (co odpowiada stanowi wysokiemu). Natomiast na wejścia nie powinny być podawane napięcia z zakresu: 0,8…2 V. Jest to obszar zabroniony, bowiem układy TTL mogą (i będą) błędnie działać w takim zakresie napięć wejściowych.

Ustalono też, że przy obciążeniu dziesięcioma wejściami TTL, na dowolnym wyjściu, w stanie niskim napięcie musi zawierać się w granicach 0…0,4 V, a w stanie wysokim 2,4…5,5 V.

Różnica między dopuszczalnymi wartościami granicznymi dla wejść i wyjść: 0,8 V−0,4 V oraz 2,4 V−2,0 V, stanowi tak zwany margines zakłóceń. Chodzi o to, że w przewodach łączących wyjścia i wejścia bramek mogą indukować się zakłócenia. Nie wpłynie to na działanie układu, jeśli tylko zakłócenia te będą mniejsze niż 0,4 V. Tu możemy odnotować kolejną istotną wadę układów TTL − mały margines zakłóceń, przy napięciu 5 V wynoszący tylko (0,4 V + 0,4 V).

Uważny Czytelnik zdążył już zaprotestować twierdząc, że przecież napięcie na wejściach i wyjściach nie może zmienić się skokowo, a więc podczas przełączania z jednego stanu logicznego do drugiego, napięcie na wejściu przez pewien czas przyjmie wartości z zabronionego przedziału: 0,8…2 V.

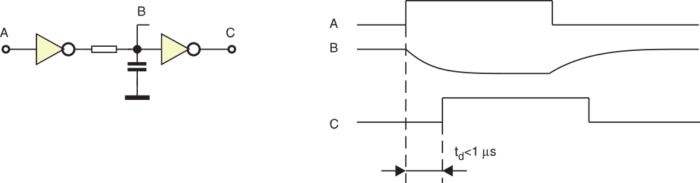

Tak jest! Ale jeśli zmiana stanu nastąpi szybko, układ zareaguje poprawnie. Jeśli natomiast napięcie będzie zmieniać się wolno, to najprawdopodobniej na wyjściu pojawią się pasożytnicze drgania. Ilustruje to rysunek 5. Powstawanie pasożytniczych drgań jest związane z dużą szybkością bramek, ich znacznym wzmocnieniem, niedoskonałym filtrowaniem napięcia zasilającego oraz kilkoma innymi czynnikami.

Jest to kolejna bardzo, naprawdę bardzo ważna sprawa. Dla uniknięcia przykrych niespodzianek, sygnały na wejściach bramek powinny zmieniać się bardzo szybko. Najprościej mówiąc, zbocza sygnałów, czyli czasy narastania i opadania powinny być krótsze niż 1 mikrosekunda.

W lewej części rysunku 5 pokazano przebiegi o prawidłowych, ostrych zboczach. Natomiast prawa część tego rysunku pokazuje przebiegi o zbyt długich czasach narastania.

Ale bez przesady − przy łączeniu układów cyfrowych zapewnienie właściwej ostrości zboczy nie jest żadnym problemem, bowiem nawet najwolniejsze układy gwarantują czasy narastania i opadania zdecydowanie krótsze niż 1 μs. Niebezpieczeństwo pojawienia się drgań grozi natomiast wtedy, gdy bramki (lub jakiekolwiek układy cyfrowe) sterowane są przez inne, wolniejsze elementy.

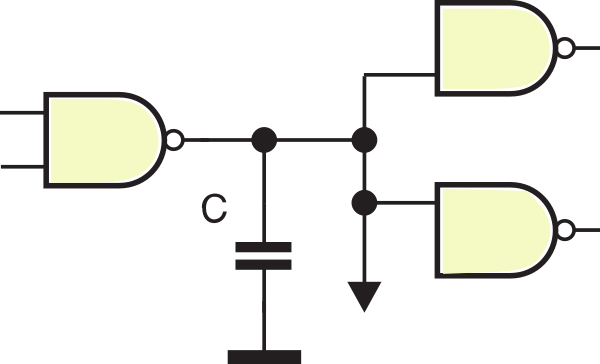

Na rysunku 6 pokazano przykład wykorzystania bramek i obwodu RC do uzyskania opóźnienia.

Wszystko będzie dobrze, jeśli czas narastania napięcia na wejściu następnej bramki nie będzie dłuższy, niż 1 μs. Przy znacznie dłuższych czasach należy liczyć się z wystąpieniem pasożytniczych drgań. Drgania te często zupełnie uniemożliwiają działanie dalszych stopni urządzenia. Sposobem pokazanym na rysunku 6 nie można więc opóźnić sygnału o czas dłuższy niż kilka mikrosekund − groziłoby to powstaniem szkodliwych drgań.

Niestety, wielu amatorów nie rozumie tego problemu − dziwią się potem, że układ czasami działa, a czasami nie. A przyczyną są właśnie dodatkowe impulsy, pojawiające się podczas zbyt łagodnych zboczy, podawanych na wejścia układów cyfrowych.

Bramki Schmitta

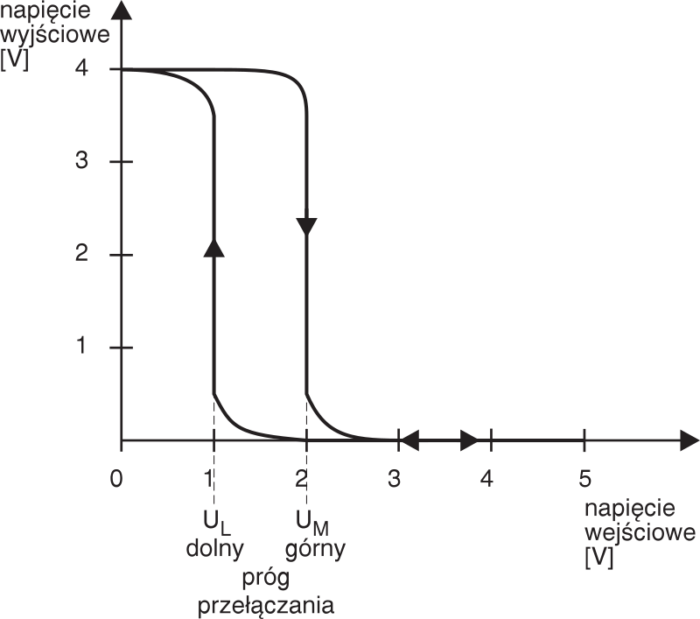

Drgania takie łatwo wyeliminować stosując bramki z histerezą. Produkuje się tak zwane bramki z wejściem Schmitta; przedstawię ci je przy prezentacji bramek. Charakterystyka przejściowa takich bramek (na przykładzie inwertera lub bramki NAND) pokazana jest w uproszczeniu na rysunku 7.

Porównaj rysunki 4 i 7, obydwa przedstawiające charakterystykę przejściową. Rzecz w tym, że w bramkach z wejściem Schmitta wprowadzono obwód histerezy i dodatniego sprzężenia zwrotnego. Przy zmianie stanu wejściowego z niskiego na wysoki, wyjście zmienia stan (z wysokiego na niski) dopiero po przekroczeniu tak zwanego górnego napięcia przełączania UM. Natomiast przy zmianie stanu na wejściu z H na L, wyjście zmienia stan dopiero, gdy na wejściu napięcie spadnie poniżej „dolnego” progu przełączania UL. Dzięki takiemu progowemu działaniu, bramki z układem Schmitta nie boją się wolno rosnących zboczy − są wręcz niezbędne, gdy do układów cyfrowych doprowadzane są wolno zmieniające się sygnały.

Bramki z wejściem Schmitta są, moim zdaniem, zbyt rzadko stosowane w konstrukcjach amatorskich − w dalszej części cyklu zaproponuję ci ich różnorodne wykorzystanie.

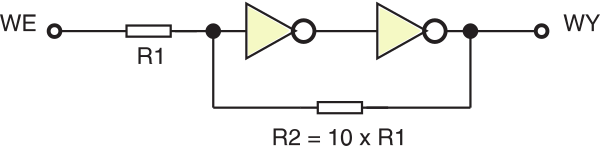

Choć produkowane są gotowe bramki z wejściem Schmitta, warto wiedzieć, że w razie potrzeby bramkę z histerezą można zrobić z dwóch negatorów (bramek NAND, NOR lub NOT) i dwóch rezystorów według rysunku 8.

Stosunek obu rezystancji wyznacza wielkość histerezy. O wartościach tych rezystorów porozmawiamy później. Teraz omówimy dokładniej problem wyjść.

Obciążalność

Skoro wejścia bramek TTL w stanie wysokim praktycznie nie pobierają prądu, więc wyjścia (współpracujące z wejściami następnych bramek) nie muszą wtedy dostarczać dużego prądu. Natomiast w stanie niskim, wyjście musi przyjąć znaczny prąd z kilku podłączonych do niego wejść – spójrz na rysunek 9.

Do wyjścia bramki TTL serii standardowej (np. 7400) można było podłączyć tylko ograniczoną ilość wejść następnych bramek tej samej serii. Przyjęto, że w stanie niskim z jednego wejścia wypływa prąd do 1,6 mA, a dowolne wyjście powinno wysterować dziesięć takich wejść. Minimalna wydajność prądowa wyjść bramek TTL standard, w stanie niskim wynosiła więc 16 mA.

Jak się łatwo domyślić na podstawie rysunku 1, wskutek obecności rezystora R4, bramki TTL miały niesymetryczną charakterystykę wyjściową. To znaczy, że wyjście w stanie niskim mogło przyjąć 30…40 mA prądu, ale w stanie wysokim mogło dostarczyć tylko kilka miliamperów (kilkanaście miliamperów przy zwarciu wyjścia do masy). Taka niesymetria miała swoje zalety − ewentualne zwarcia wyjść do masy nie powodowały uszkodzenia układu scalonego. Jeśli uważasz, że wydajność prądowa w stanie wysokim mogłaby być jeszcze o wiele mniejsza, jesteś w błędzie. Czy wiesz dlaczego?

Otóż w realnych układach, musimy jeszcze uwzględnić szkodliwe pojemności montażowe, zarówno pojemności wejściowe, jak i pojemności między ścieżkami, a masą. W sumie możemy sobie wyobrazić, że do każdego wyjścia podłączona jest szkodliwa pojemność, rzędu kilkunastu−kilkudziesięciu pikofaradów, jak pokazano to na rysunku 10.

Wprawdzie pojemność ta jest względnie niewielka, ale jak by nie było, prąd wyjściowy bramki musi przy każdej zmianie stanu, naładować lub rozładować tę pojemność. Jeśli prąd wyjściowy w stanie wysokim byłby niewielki, okazałoby się, że czas ładowania tej pojemności jest większy niż czas opóźnienia bramki. W takiej sytuacji nie można byłoby wykorzystać znacznej szybkości bramek. Trzeba wiedzieć, że czas opóźnienia bramki TTL wynosi około 10 nanosekund (miliardowych części sekundy), co umożliwia pracę z częstotliwościami rzędu kilkudziesięciu megaherców. Dla w miarę szybkiego naładowania wspomnianej szkodliwej pojemności, wydajność prądowa wyjścia w stanie wysokim też musiała być znaczna.

Typy wyjść

Wyjście takie, jak pokazano na rysunku 1, w literaturze nazywa się wyjściem „totem pole” (w skrócie TP), co w wolnym tłumaczeniu znaczy słup totemowy.

Przy tej okazji wspomnijmy jeszcze o bramkach z wyjściem typu otwarty kolektor, w skrócie OC. Na przykład kostka 7401 zawiera cztery bramki NAND z takim wyjściem. Bramka z wyjściem OC nie ma tranzystora T4, diody D1 i rezystora R4, a tylko tranzystor T3 wyjściu (patrz rysunek 1). Choć mówiłem ci, że pozostawienie wejść bramki TTL „w powietrzu” odpowiada stanowi wysokiemu, jednak ze względu na zakłócenia oraz konieczność przeładowania szkodliwych pojemności (rysunek 10), konieczne jest zastosowanie tak zwanego rezystora podciągającego (w literaturze spotkasz określenie pull−up resistor). Bramki z otwartym kolektorem umożliwiają w prosty sposób zrealizowanie funkcji AND lub OR „na drucie” (angielskie określenie: wired−AND lub wired−OR). Zauważ, że przy połączeniu pokazanym na rysunku 11, stan wyjścia zmienia się, gdy wszystkie bramki mają stan wyjściowy wysoki (tranzystory wyjściowe nie przewodzą) − zrealizowana jest funkcja AND. Inaczej mówiąc, stan wyjścia zmienia się, gdy przynajmniej jeden z tranzystorów wyjściowych zaczyna przewodzić − daje to działanie podobne do bramki OR.

Zauważ, że stosując bramki z otwartym kolektorem pracujące na wspólny rezystor, łączymy kilka wyjść ze sobą i niczym to nie grozi, a wprost przeciwnie,realizujemy przy okazji pożyteczne funkcje. Nie wolno natomiast łączyć ze sobą wyjść typu „totem pole” − gdy jedno wyjście ma stan wysoki, a inne niski, wtedy między nimi płynie znaczny prąd. Prąd ten nie tylko zwiększa straty − przy połączeniu kilku bramek może to doprowadzić do uszkodzenia któregoś wyjścia. Od tej reguły jest jeden wyjątek − dla zwiększenia wydajności prądowej wyjścia, można łączyć kilka bramek „równolegle”, ale tylko wtedy, gdy są to bramki (inwertery) z tej samej kostki − patrz rysunek 12.

Przy „równoległym” łączeniu bramek z różnych kostek zachodzi obawa, że ich czasy opóźnienia mogą być różne, co spowoduje niejednoczesne przełączanie i niepotrzebny wzrost poboru prądu.

Ponieważ często (zwłaszcza w technice komputerowej) kilka źródeł sygnału, czyli po prostu wyjść, dołączonych jest do wspólnej szyny przesyłowej, opracowano układy z tak zwanym wyjściem trójstanowym. Schemat wewnętrzny jest podobny do układu totem pole z tym, że dodano obwód sterujący pracą tranzystorów wyjściowych. W efekcie oprócz stanu L i H, na wyjściu występuje tak zwany stan trzeci, oznaczany zwykle literą Z, w którym oba tranzystory wyjściowe (T3 i T4 na rysunku 1) nie przewodzą. Wtedy dana bramka jest zupełnie odcięta od wspólnej szyny. W kostkach z takim trzystanowym wyjściem zawsze występuje dodatkowe wejście sterujące − wejście zezwalające, oznaczane OE (Output Enable). Wyjście trójstanowe (ang. tristate) oznaczane jest w literaturze skrótem TS.

Masz już komplet wiadomości o standardowych bramkach TTL i trochę ważnych informacji dodatkowych. Materiału tego nie musisz zapamiętywać, ale powinieneś go dobrze rozumieć. Wszystko to jest ci potrzebne, żebyś dobrze zrozumiał działanie i właściwości kostek stosowanych obecnie.

Inne rodziny

Kostki standardu TTL, z czołowym przedstawicielem 7400, były w swoim czasie rewelacją. Pojedyncza bramka zasilana napięciem 5 V pobierała tylko kilka miliamperów prądu i była szybka − czas propagacji, czyli opóźnienia między wejściem, a wyjściem, wynosił około 10 ns. Wkrótce okazało się, że te parametry wcale się są rewelacyjne. Nie wszędzie potrzebne były tak szybkie układy, a za to pożądane byłyby kostki pobierające znacznie mniej prądu. Gdzie indziej potrzebne były kostki jeszcze szybsze. Jeszcze gdzie indziej, w warunkach dużych zakłóceń przemysłowych, potrzebne były kostki z dużo większym marginesem zakłóceń.

Pierwszym krokiem w realizacji tych potrzeb było wypuszczenie układów serii 74L. Litera L pochodzi od Low Power − mała moc. Układ wewnętrzny był taki sam, jak standardowych kostek rodziny 74 (patrz rysunek 1), dziesięciokrotnie zwiększono tylko wartości wewnętrznych rezystorów. Kostka pobierała dziesięciokrotnie mniej prądu, miała dziesięciokrotnie mniejszy prąd wejściowy w stanie niskim, ale była kilkakrotnie razy wolniejsza i miała małą wydajność prądową wyjść − w stanie niskim 3,2 mA, w wysokim 0,18 mA (w serii standardowej 74 wartości wynosiły nominalnie odpowiednio: 30 i 1,8 mA). Z tego widać, że wyjście bramki rodziny 74L mogło wysterować tylko dwa wejścia standardowej bramki 74.

Wypuszczono też rodzinę 74H. Litera H pochodzi od określenia High Speed − duża szybkość. W tej rodzinie zmniejszono wewnętrzne rezystancje. Układy tej rodziny (np. 74H00, 74H72, 74H93) były trochę szybsze od standardowych, pobierały dwukrotnie więcej prądu, a i prąd wejściowy w stanie niskim był dwukrotnie większy. Wydajność wyjść była zbliżona do bramek standardowych. Znacznie większą szybkość, około trzykrotnie większą od standardowych, przy poborze prądu takim jak bramki rodziny 74H, miały bramki rodziny 74S (np. 74S00, 74S112). Litera S pochodzi od nazwiska Schottky (czytaj − szotki). W konstrukcji układów tej rodziny zastosowano w tranzystorach złącza Schottky’ego. Szczegóły nie są najważniejsze − dzięki tym złączom tranzystory nie wchodziły głęboko w stan nasycenia i w efekcie były znacznie szybsze od zwykłych tranzystorów. Kostki te miały prądy wejściowe i wyjściowe zbliżone do kostek rodziny 74H.

Dziś wszystkie kostki z rodzin: 74, 74L, 74H i 74S są dinozaurami i według mojej wiedzy nikt już ich nie produkuje.

Opowiedziałem ci o nich, bo zapewne natkniesz się na nie przy rozbiórce starego sprzętu. Powinieneś więc wiedzieć, że wszystkie kostki o tym samym numerze, pochodzące z różnych rodzin (np. 7490, 74L90, 74H90) mają taki sam rozkład wyprowadzeń i różnią się w sumie tylko poborem prądu i wielkością prądów wejściowych i wyjściowych.

Oznaczenia układów TTL

Pierwsza cyfra oznaczenia wskazuje na dopuszczalny zakres temperatur pracy. I tak 7 to przedział 0…+70°C, 6: −40…+85°C, a 5: −55…+125°C.

Ogromna większość kostek ma oczywiście najwęższy zakres pracy i pierwszą cyfrę 7. Rzadko, ale spotyka się kostki do zastosowań przemysłowych z pierwszą cyfrą 6, na przykład 6400, czy 64LS90. Są to ścisłe odpowiedniki kostek 7400 i 74LS90, z tym, że mogą pracować w szerszym zakresie temperatur. Natomiast rzadziej można spotkać kostki z serii militarnej z pierwszą cyfrą 5, np. 5400, czy 54LS90.

Druga cyfra oznaczenia w układach logicznych z rodzin TTL to zawsze 4.

Dwie, czasem trzy, bardzo rzadko cztery, kolejne cyfry wskazują na typ i funkcje układu. Nie ma tu jakiegoś prostego klucza − z czasem każdy elektronik zapamiętuje popularniejsze kostki. Nie ucz się na pamięć takich oznaczeń − od tego są katalogi. Musisz tylko wiedzieć, że kostki o jednakowych ostatnich cyfrach oznaczenia mają taki sam układ wyprowadzeń, na przykład: 54121, 64LS121, 64L121, 74S121, itd.

Wiesz już, że litery w środku oznaczenia wskazują na rodzinę, czyli określają budowę wewnętrzną i technologię produkcji.

Natomiast litery na początku oznaczenia wskazują tylko producenta i często przy określaniu kostki są pomijane. Jeśli w spisie elementów podano, że w układzie masz zastosować kostkę LS14, to bez obawy możesz użyć kostek z dowolnymi literkami na początku, np.: MM74LS14, UCY74LS14, CD74LS14, GD74LS14, itp.

Często oznaczenie ma jeszcze literę lub litery na końcu, np.: UCY64H74J, UCY74S00N, SN74LS27D. Ostatnia litera(y) oznacza zwykle typ obudowy. Litera N wskazuje za zwykłą, typową obudowę plastikową typu DIL, litera J − obudowę ceramiczną, o lepszych właściwościach cieplnych, litera D − miniaturową obudowę do montażu powierzchniowego.

W sumie z całego oznaczenia dla praktyka znaczenie mają przede wszystkim litery między cyframi i ostatnie cyfry oznaczenia. Dlatego powszechnie zamiast pisać: UCY74LS90N, podaje się krótko LS90, zamiast CD74123 pisze się 123, zamiast MM74S112 pisze się S112, itd.

Szczegóły na temat możliwości zamiany kostek z różnych rodzin podam ci trochę później.

A kolejny odcinek cyklu znajdziesz tutaj.

Piotr Górecki