Wspólnie projektujemy: Częstościomierz, część 3

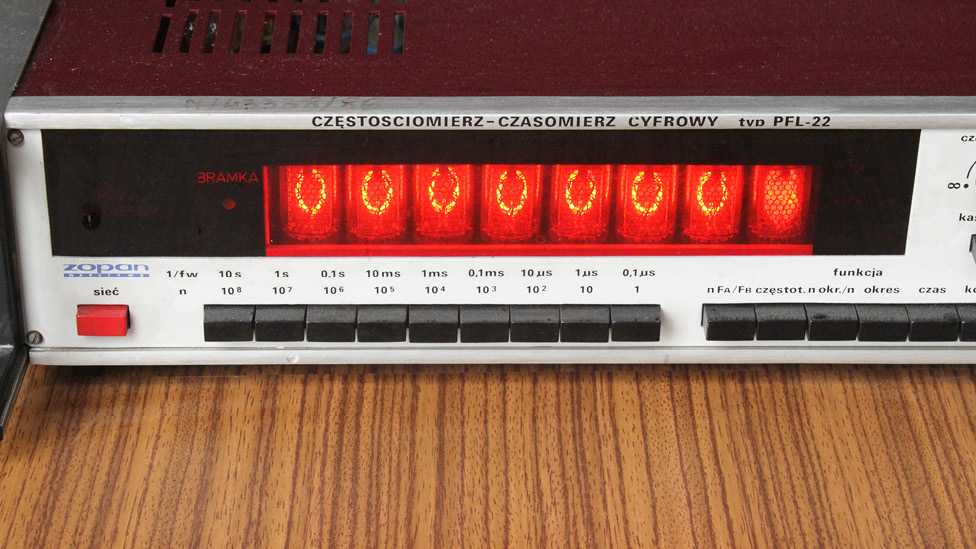

W poprzedniej części, jako ciekawostka, została zaprezentowana konstrukcja rodem z ubiegłego wieku. Obecnie, również jako ciekawostkę, zaprezentuję połączenie „starożytnej” klasyki z nowoczesnością, czyli implementacja częstościomierza w środowisku układów logiki programowalnej.

Układy PLD

Tematyka związana z układami PLD (ang. Programmable Logic Device), czyli układów cyfrowych o programowalnej strukturze jest bardzo obszerna. Jednak przed omówieniem rozwiązania konieczne jest elementarne wprowadzenie w świat układów PLD. Są to elementy cyfrowe, które można skonfigurować by realizowały oczekiwaną funkcję. W języku polskim pewne wyrazy mają wiele znaczeń i taki właśnie przypadek tu zaistniał. Pomimo że czynność „programować” w stosunku do tego układu jest w pełni uzasadniona, jednak pod pojęciem programowania kryje się całkowicie odmienna operacja niż w przypadku mikroprocesorów. „Program” dla układów PLD nie zawiera w sobie kodów instrukcji do wykonania, a jedynie informacje dotyczące połączeń pomiędzy wewnętrznymi elementami (zasobami układu). Na programowanie można również spojrzeć z perspektywy „wbicia” kodu do pamięci układu. Tu taka operacja występuje – za pomocą odpowiedniego oprogramowania tworzy się „wsad” dla takiego układu, który należy umieścić w jego wnętrzu. Zaprogramowane dane określają co z czym ma być połączone w jego wnętrzu.

Układy PLD można podzielić na dwie podstawowe rodziny: CPLD (ang. Complex Programmable Logic Device – złożone układy programowalne) oraz FPGA (ang. Field-Programmable Gate Array – programowalna matryca bramek). Różnią się one przede wszystkim wielkością zasobów (FPGA ma wręcz ogromne zasoby) oraz technologią wykonania. Z punktu widzenia użytkownika jedne i drugie dają się konfigurować, używa się tego samego języka do opisu układu a różnica „użytkowa” to taka, że FPGA są bardziej elastyczne oraz mają znacząco większe zasoby.

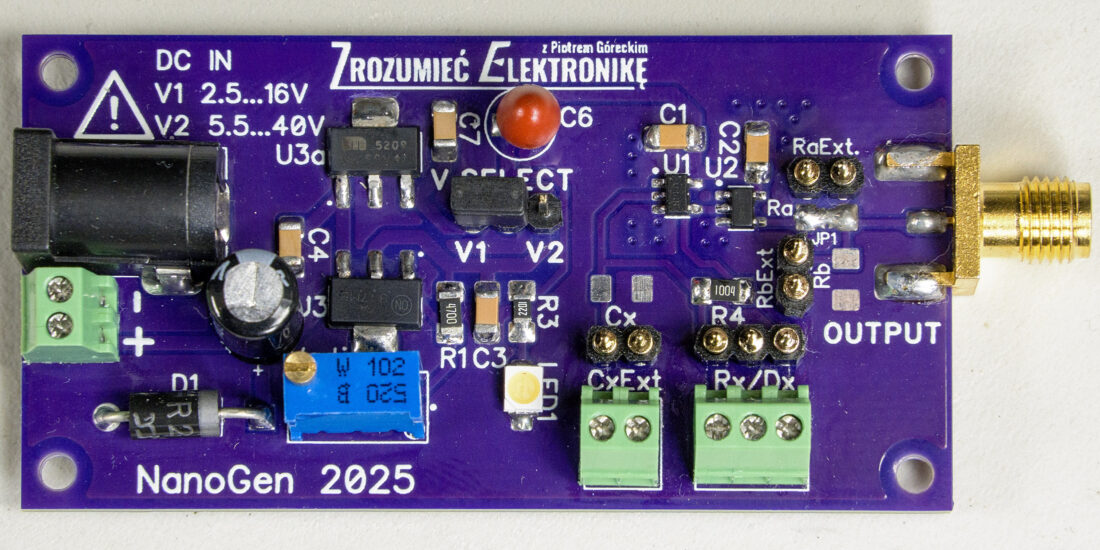

Do konstrukcji zostaje użyty układ CPLD z oferty Xilinx o oznaczeniu XC95144XL (fotografia 1), do konfiguracji którego zastosowany jest język VHDL (oczywiście są i inne języki).

Te układy „obrabia się” za pomocą dedykowanego oprogramowania (tylko dla układów Xilinx). Można je pobrać ze strony www.xilinx.com. Sama firma chwali się, że pakiet WebPack jest jedynym komercyjnym oprogramowaniem projektowym, które jest bezpłatne. Dokładniej, to wymagana jest licencja, którą można bezpłatnie uzyskać od Xilinx na okres roku (można ją przedłużać). Obecnie dostępna jest wersja o numerze 14. Ja w poniższym projekcie używam wersji o numerze 7.2, która ma już swoje lata. Ta wersja dla mnie jest niejako bezcenna, gdyż w chwili wejścia jej do użytku firma Xilinx udzielała licencji na jej użycie bez limitu daty. Można powiedzieć, że obecnie mam dożywotnią licencję na pracę z tym programem (nowsze mają jedynie większą ofertę „obrabianych” układów, a „stara” całkowicie mi wystarcza w moich zastosowaniach).

Stare w nowym wydaniu

W odpowiedzi na moją prośbę, kolega Krzysztof Markowski udostępnił swój projekt do wykorzystania. Przeanalizowałem jego rozwiązanie, do którego wniosłem kilka modyfikacji, gdyż tu nie wykorzystujemy gotowych układów scalonych TTL (które są jakie są) a tworzymy własne, niejako wirtualne układy scalone (które sami kształtujemy). W metodologii projektowej można wyróżnić dwie metody podejścia: „od ogółu do szczegółu” (patrzymy na całość wyróżniając pewne bloki funkcjonalne, które są dalej uszczegóławiane) lub „od szczegółu do ogółu” (zaczynamy od detali i tworzymy coraz bardziej złożone struktury).

Jedną z modyfikacji, którą wniosłem do projektu jest dodanie globalnego sygnału wejściowego Reset, który ustawia wszystkie liczniki i przerzutniki do stanu początkowego (jego stan aktywny to logiczne zero). To bardziej jest potrzebne ze względu na użycie układów PLD, układy TTL „mają swoje przyzwyczajenia” i po włączeniu zasilania ustawiają się we właściwy sposób, układy PLD wymagają podania wszystkich szczegółów.

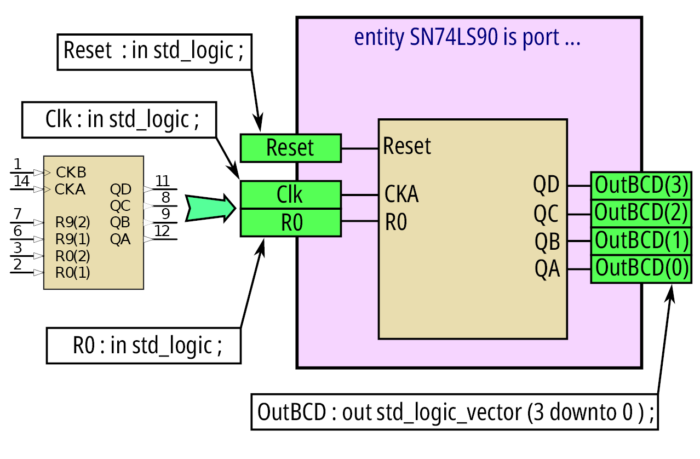

Częstościomierz składa się przede wszystkim z liczników dziesiętnych (SN74LS90), toteż w pierwszej kolejności zostanie zamodelowany ten układ (opiszemy w języku VHDL działanie takiego elementu).

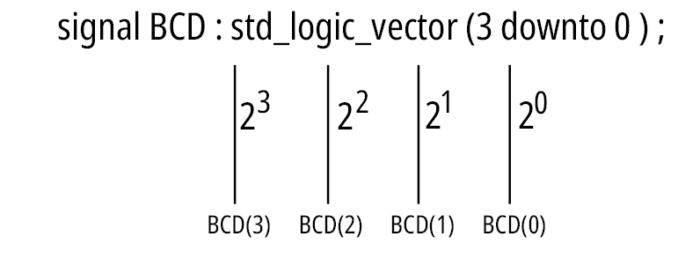

Zanim do tego przejdziemy – kilka słów wyjaśnień. Każdy sygnał (czyli drucik) ma swoją nazwę, po której identyfikowane jest połączenie. Typowy pojedynczy sygnał jest określany jako std_logic. W przypadku stosowania magistral (kilku równoległych drucików, są one wtedy numerowane), należy je określić jako std_logic_vector oraz podać zakres indeksów. Tutaj używa się określenia std_logic_vector (<liczba> to <liczba>) lub std_logic_vector (<liczba> downto <liczba>). Różnica (to/downto) dotyczy kierunku numeracji. Zwyczajowo skrajnie lewy sygnał ma najwyższą wagę (jest najbardziej znaczący) natomiast prawy ma najniższą wagę. By uzyskać zgodność numeru drucika z wagą binarną należy użyć sformułowania downto. Bit (drucik) najbardziej znaczący (skrajnie lewy) ma najwyższy indeks i każdy kolejny mniej znaczący (lokowany w prawą stronę) ma dekrementowany indeks. Ideę pokazuje rysunek 2.

Pomijając stały fragment (library…, use…) określających użyte specyfikacje i typy, każdy komponent, taki wirtualny układ scalony, zaczyna się od „entity <nazwa> is port (lista sygnałów wejściowych lub wejściowych danego komponentu)”. Ta lista sygnałów jest odpowiednikiem wyprowadzeń naszego wirtualnego układu scalonego. Dalej (za architecture) wymieniana jest lokalna lista użytych sygnałów, czasem innych użytych wirtualnych układów oraz w dalszej części (za begin) następuje opis danego komponentu. Często w opisie (za begin od architecture) występuje zapis process. Ten fragment (aż do end process) opisuje element sekwencyjny, który w dużym uproszczeniu można uważać za coś reagującego na sygnał zegarowy (przerzutnik, licznik, rejestr).

Licznik

Budowę licznika dziesiętnego symbolicznie pokazuje rysunek 3.

(…)

——– ciach! ——–

To jest tylko fragment artykułu, którego pełna wersja ukazała się w numerze styczniowym czasopisma Zrozumieć Elektronikę (ZE 2/2024). Pełną wersję czasopisma znajdziesz pod tym linkiem. Natomiast niepełna, okrojona wersja, pozwalająca zapoznać się z zawartością numeru ZE 2/2024 znajduje się tutaj.

Andrzej Pawluczuk

apawluczuk@vp.pl

Uwaga! Wskazówki, jak nabyć archiwalne numery znajdują się na stronie: https://piotr-gorecki.pl/n11

.