Zapisane w pamięci – historia i typy pamięci, część 3

Obecnie pamięci operacyjne są budowane na bazie pamięci dynamicznych. Jest to odmiana funkcjonalna wcześniej opisanych układów statycznych RAM. Ich budowa i sposób obsługi jest znacząco odmienny od rozwiązań statycznych, toteż poświęcony jest temu niezależny artykuł.

W czasach, gdy były konstruowane pierwsze komputery przeznaczone do zastosowań domowych, koszt pamięci statycznych był wysoki. Upowszechnienie się komputerów osobistych (komputery PC), a wcześniej komputerów przewidzianych raczej do gier (Spectum, Commodore czy Atari), było możliwe dzięki opracowaniu tanich układów pamięci dynamicznych o dużej pojemności (koszt jednego kilobajta pamięci dynamicznej jest znacząco mniejszy od wariantu statycznego).

Koncepcja budowy pamięci dynamicznej RAM

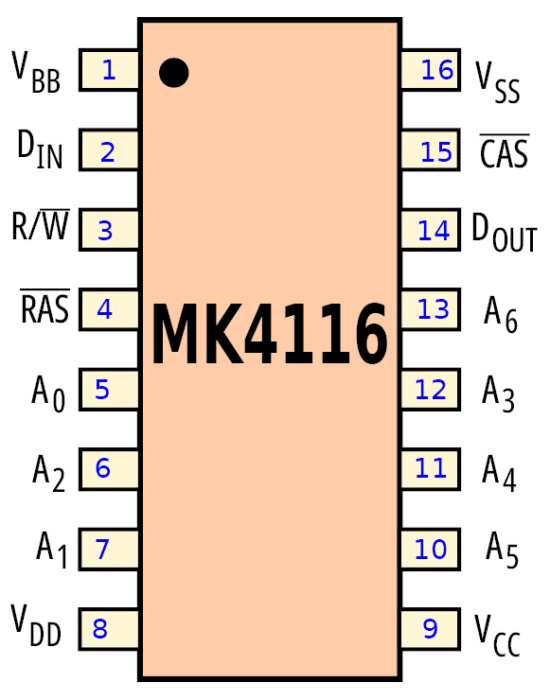

Nośnikiem informacji zapisanej w pamięci może być stan przerzutnika (jak w statycznych pamięciach RAM) lub stan naładowania kondensatora jak w pamięciach DRAM (ang. Dynamic Random-Access Memory – dynamiczna pamięć o dostępie swobodnym). Niestety kondensatory mają tę własność, że z czasem rozładowują się. Dodatkowo sama operacja odczytu również uszczupla zgromadzony w kondensatorze ładunek. Aby nie utracić zapisanej informacji, koniecznością staje się jej odświeżanie (to nic innego jak ponowny zapis informacji: doładowanie kondensatora jeżeli był naładowany). Obok normalnego cyklu zapisu/odczytu danych (jak w pamięciach statycznych), który w pamięciach dynamicznych stanowił jednocześnie operację odświeżenia, tutaj została dodana operacja samego odświeżenia (nie mająca na celu udostępnienie danych na zewnątrz, jak przy odczycie). Pierwszym układem, który zdobył uznanie wśród konstruktorów była pamięć o symbolu MK4116 (rysunek 1), pomimo że miała ona jedną wadę – wymagała trzech napięć zasilających (VBB to – 5 V, VDD to +12 V a VCC to +5 V), VSS (inaczej GND) to potencjał odniesienia – masa.

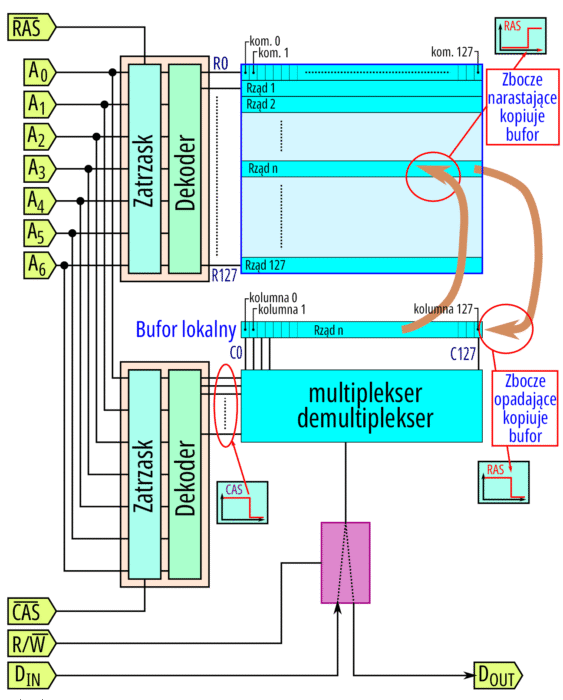

Była to pamięć dynamiczna o pojemności 16 k × 1 (była jednobitowa, należało połączyć równolegle osiem układów, by uzyskać organizację bajtową). Jeśli uważnie się przyjrzeć układowi, to łatwo zauważyć, że liczba linii adresowych jest znacząco za mała by układ był w stanie rozróżnić 16 384 różnych kombinacji adresowych (do zaadresowania tej przestrzeni niezbędne jest 14 linii adresowych). Dodatkowo nie ma tu sygnału o funkcji CS (chip select), znanego z pamięci statycznych, oraz występują dwa nowe tajemnicze: RAS (ang. Row Address Strobe – strob adresu rzędu) i CAS (ang. Column Address Strobe – strob adresu kolumny), stanem aktywnym linii RAS i CAS jest zero logiczne. Wszystkie te elementy są ściśle związane ze specyfiką budowy i działania pamięci dynamicznych. Wyobraźmy sobie kwadratową matrycę komórek pamięci. Podanie na linie adresowe (w MK4116 to będzie A0…A6) kombinacji bitowej odpowiadającej połowie (w sensie liczby linii) adresu komórki. Wystąpienie sygnału RAS=0 (wybór rzędu w kwadratowej matrycy komórek) w wyniku wewnętrznego dekodowania prowadzi do przepisania całego rzędu z matrycy do lokalnego statycznego bufora. „Zanik” tego sygnału (przejście z RAS=0 do RAS=1) powoduje przepisanie z lokalnego bufora do kwadratowej matrycy. To przepisanie jednocześnie jest operacją odświeżenia danych w pamięci. Jeden impuls na linii RAS prowadzi do odświeżenia 128 komórek pamięci (jednego rzędu). Teraz niech wystąpi bardziej złożone sterowanie. Analogicznie jak poprzednio, po podaniu kombinacji bitowej na linie adresowe następuje zbocze opadające na linii RAS. To jak dotychczas prowadzi do przekopiowania jednego z rzędów matrycy pamięci do lokalnego bufora. Teraz następuje zmiana adresu (na drugą połowę linii adresowych w sensie sztuk) i następnie linia CAS zmienia stan: jest zbocze opadające. To oznacza, że z lokalnego bufora jest wyselekcjonowana jedna komórka (identyfikowana przez adres występujący w chwili opadającego zbocza CAS) i jest ona przesłana do wyprowadzenia DOUT – jako operacja odczytu lub z linii DIN stan jest przepisany do lokalnego bufora – jako operacja zapisu. Ten rodzaj operacji jest identyfikowany stanem linii R/W (identycznie jak w pamięciach statycznych: R/W=1 oznacza odczyt, R/W=0 oznacza zapis). Zmiana stanu linii RAS (z RAS=0 na RAS=1) prowadzi do przepisania lokalnego bufora do matrycy wszystkich komórek (jeżeli była operacja zapisu, to bufor lokalny zawiera zmieniony stan bitu, który trafi do matrycy). Oprócz specjalnego cyklu odświeżenia danych (operacja tylko z sygnałem RAS), każdy odczyt lub zapis również prowadzi do odświeżenia całego rzędu matrycy pamięci. Koncepcję ilustruje rysunek 2.

(…)

——– ciach! ——–

To jest tylko fragment artykułu, którego pełna wersja ukazała się w listopadowym numerze czasopisma Zrozumieć Elektronikę (ZE 11/2025). Pełną wersję czasopisma znajdziesz pod tym linkiem. Natomiast niepełna, okrojona wersja, pozwalająca zapoznać się z zawartością numeru ZE 11/2025 znajduje się tutaj.

Andrzej Pawluczuk

apawluczuk@vp.pl

Uwaga! Wskazówki, jak nabyć pełne wersje dowolnych numerów ZE znajdują się na stronie:

https://piotr-gorecki.pl/n11.